# Digital Design and Computer Architecture RISC-V Edition

Sarah L Harris David Money Harris

#### **Table B.4** Register names and numbers

| Name  | Register<br>Number | Use                                |

|-------|--------------------|------------------------------------|

| zero  | x0                 | Constant value 0                   |

| ra    | x1                 | Return address                     |

| sp    | x2                 | Stack pointer                      |

| gp    | x3                 | Global pointer                     |

| tp    | x4                 | Thread pointer                     |

| t0-2  | x5-7               | Temporary registers                |

| s0/fp | x8                 | Saved register / Frame pointer     |

| s1    | x9                 | Saved register                     |

| a0-1  | x10-11             | Function arguments / Return values |

| a2-7  | x12-17             | Function arguments                 |

| s2-11 | x18-27             | Saved registers                    |

| t3-6  | x28-31             | Temporary registers                |

| 15 14 13 | 12     | 11  | 10  | 9    | 8      | 7  | 6     | 5   | 4 | 3     | 2  | 1 | 0    |          |

|----------|--------|-----|-----|------|--------|----|-------|-----|---|-------|----|---|------|----------|

| funct4   |        |     | rd  | /rs1 |        |    | rs2   |     |   |       |    | c | р    | CR-Type  |

| funct3   | imm    |     | rd  | /rs1 |        |    | imr   | n   |   |       |    | C | р    | CI-Type  |

| funct3   | imm    |     |     |      | rs1'   |    | imr   | n   |   | rs2   | 2' | C | р    | CS-Type  |

| funct6   |        |     |     | rd   | l'/rs  | 1' | fun   | ct2 |   | rs2   | 2' | C | р    | CS'-Type |

| funct3   | imm    |     |     |      | rs1'   |    | imr   | n   |   |       |    | C | р    | CB-Type  |

| funct3   | imm    | fui | nct | rd   | l'/rs  | 1' | imr   | n   |   |       |    | C | р    | CB'-Type |

| funct3   | imm    |     |     |      |        |    |       |     |   |       |    | C | р    | CJ-Type  |

| funct3   | imm    |     |     |      |        |    | rs2   |     |   |       |    | C | р    | CSS-Type |

| funct3   | imm    |     |     |      |        |    |       |     |   | rd'   |    | C | р    | CIW-Type |

| funct3   | imm    |     |     |      | rs1'   |    | imr   | n   |   | rd'   |    | C | р    | CL-Type  |

| 3 bits   | 3 bits |     |     |      | 3 bits |    | 2 bit | s   |   | 3 bit | s  | 2 | bits | •        |

Figure B.2 RISC-V compressed (16-bit) instruction formats

#### Table B.5 RVM: RISC-V multiply and divide instructions

| op           | funct3 | funct7  | Type | Instruction         | Description                     | Operation                  |

|--------------|--------|---------|------|---------------------|---------------------------------|----------------------------|

| 0110011 (51) | 000    | 0000001 | R    | mul rd, rs1, rs2    | multiply                        | $rd = (rs1 * rs2)_{31:0}$  |

| 0110011 (51) | 001    | 0000001 | R    | mulh rd, rs1, rs2   |                                 | $rd = (rs1 * rs2)_{63:32}$ |

| 0110011 (51) | 010    | 0000001 | R    | mulhsu rd, rs1, rs2 | multiply high signed unsigned   | $rd = (rs1 * rs2)_{63:32}$ |

| 0110011 (51) | 011    | 0000001 | R    | mulhu rd, rs1, rs2  | multiply high unsigned unsigned | $rd = (rs1 * rs2)_{63:32}$ |

| 0110011 (51) | 100    | 0000001 | R    | div rd, rs1, rs2    | divide (signed)                 | rd = rs1 / rs2             |

| 0110011 (51) | 101    | 0000001 | R    | divu rd, rs1, rs2   | divide unsigned                 | rd = rs1 / rs2             |

| 0110011 (51) | 110    | 0000001 | R    | rem rd, rs1, rs2    | remainder (signed)              | rd = rs1 % rs2             |

| 0110011 (51) | 111    | 0000001 | R    | remu rd, rs1, rs2   | remainder unsigned              | rd = rs1 % rs2             |

#### Table B.6 RVC: RISC-V compressed (16-bit) instructions

|        | lable B.6 KVC: RISC-V compressed (16-bit) instructions |        |      |                                           |                                              |  |  |  |

|--------|--------------------------------------------------------|--------|------|-------------------------------------------|----------------------------------------------|--|--|--|

| op     | instr <sub>15:10</sub>                                 | funct2 | Type | RVC Instruction                           | 32-Bit Equivalent                            |  |  |  |

| 00 (0) | 000                                                    | _      | CIW  | c.addi4spn rd', sp, imm                   | addi rd', sp, ZeroExt(imm)*4                 |  |  |  |

| 00 (0) | 001                                                    | _      | CL   | c.fld fd', imm(rs1')                      | fld fd', (ZeroExt(imm)*8)(rs1')              |  |  |  |

| 00 (0) | 010                                                    | _      | CL   | c.lw rd', imm(rs1')                       | <pre>lw rd', (ZeroExt(imm)*4)(rs1')</pre>    |  |  |  |

| 00 (0) | 011                                                    | _      | CL   | c.flw fd', imm(rs1')                      | flw fd', (ZeroExt(imm)*4)(rs1')              |  |  |  |

| 00(0)  | 101                                                    | _      | CS   | c.fsd fs2', imm(rs1')                     | fsd fs2', (ZeroExt(imm)*8)(rs1')             |  |  |  |

| 00(0)  | 110                                                    | _      | CS   | c.sw rs2', imm(rs1')                      | sw rs2', (ZeroExt(imm)*4)(rs1')              |  |  |  |

| 00(0)  | 111                                                    | _      | CS   | c.fsw fs2', imm(rs1')                     | fsw fs2', (ZeroExt(imm)*4)(rs1')             |  |  |  |

| 01(1)  | 000000                                                 | _      | CI   | c.nop (rs1=0,imm=0)                       | nop                                          |  |  |  |

| 01(1)  | 000                                                    | _      | CI   | c.addi rd, imm                            | addi rd, rd, SignExt(imm)                    |  |  |  |

| 01(1)  | 001                                                    | _      | CJ   | c.jal label                               | jal ra, label                                |  |  |  |

| 01(1)  | 010                                                    | _      | CI   | c.li rd, imm                              | addi rd, xO, SignExt(imm)                    |  |  |  |

| 01(1)  | 011                                                    | _      | CI   | c.lui rd, imm                             | lui rd, $\{14\{\text{imm}_5\}, \text{imm}\}$ |  |  |  |

| 01(1)  | 011                                                    | _      | CI   | c.addi16sp sp, imm                        | addi sp, sp, SignExt(imm)*16                 |  |  |  |

| 01(1)  | 100-00                                                 | _      | CB'  | c.srli rd', imm                           | srli rd', rd', imm                           |  |  |  |

| 01(1)  | 100-01                                                 | _      | CB'  | c.srai rd', imm                           | srai rd', rd', imm                           |  |  |  |

| 01(1)  | 100-10                                                 | -      | CB'  | c.andi rd', imm                           | andi rd', rd', SignExt(imm)                  |  |  |  |

| 01(1)  | 100011                                                 | 00     | CS'  | c.sub rd', rs2'                           | sub rd', rd', rs2'                           |  |  |  |

| 01(1)  | 100011                                                 | 01     | CS'  | c.xor rd', rs2'                           | xor rd', rd', rs2'                           |  |  |  |

| 01(1)  | 100011                                                 | 10     | CS'  | c.or rd', rs2'                            | or rd', rd', rs2'                            |  |  |  |

| 01(1)  | 100011                                                 | 11     | CS'  | c.and rd', rs2'                           | and rd', rd', rs2'                           |  |  |  |

| 01(1)  | 101                                                    | _      | CJ   | c.j label                                 | jal xO, label                                |  |  |  |

| 01(1)  | 110                                                    | _      | CB   | c.beqz rs1', label                        | beq rs1', x0, label                          |  |  |  |

| 01(1)  | 111                                                    | _      | СВ   | c.bnez rs1', label                        | bne rs1', x0, label                          |  |  |  |

| 10(2)  | 000                                                    | _      | CI   | c.slli rd, imm                            | slli rd, rd, imm                             |  |  |  |

| 10(2)  | 001                                                    | _      | CI   | c.fldsp fd, imm                           | fld fd, (ZeroExt(imm)*8)(sp)                 |  |  |  |

| 10(2)  | 010                                                    | _      | CI   | c.lwsp rd, imm                            | lw rd, (ZeroExt(imm)*4)(sp)                  |  |  |  |

| 10(2)  | 011                                                    | _      | CI   | c.flwsp fd, imm                           | flw fd, (ZeroExt(imm)*4)(sp)                 |  |  |  |

| 10(2)  | 1000                                                   | _      | CR   | c.jr rs1 (rs1≠0,rs2=0)                    | jalr x0, rs1, 0                              |  |  |  |

| 10(2)  | 1000                                                   | _      | CR   | c.mv rd, rs2 (rd $\neq 0$ ,rs2 $\neq 0$ ) | add rd, x0, rs2                              |  |  |  |

| 10(2)  | 1001                                                   | _      | CR   | c.ebreak (rs1=0,rs2=0)                    |                                              |  |  |  |

| 10(2)  | 1001                                                   | _      | CR   | c.jalr rs1 (rs1≠0,rs2=0)                  | jalr ra, rs1, 0                              |  |  |  |

| 10(2)  | 1001                                                   | _      | CR   | c.add rd, rs2 (rs1≠0,rs2≠0)               | add rd, rd, rs2                              |  |  |  |

| 10(2)  | 101                                                    | _      | CSS  | c.fsdsp fs2, imm                          | fsd fs2, (ZeroExt(imm)*8)(sp)                |  |  |  |

| 10(2)  | 110                                                    | -      | CSS  | c.swsp rs2, imm                           | sw rs2, (ZeroExt(imm)*4)(sp)                 |  |  |  |

| 10(2)  | 111                                                    | -      | CSS  | c.fswsp fs2, imm                          | fsw fs2, (ZeroExt(imm)*4)(sp)                |  |  |  |

**Table B.7 RISC-V pseudoinstructions**

| Pseudoinstruction          | RISC-V Instructions                                                                 | Description                        | Operation                             |

|----------------------------|-------------------------------------------------------------------------------------|------------------------------------|---------------------------------------|

| nop                        | addi x0, x0, 0                                                                      | no operation                       |                                       |

| li rd, $imm_{11:0}$        | addi rd, x0, imm <sub>11:0</sub>                                                    | load 12-bit immediate              | rd = SignExtend(imm <sub>11:0</sub> ) |

| li rd, imm <sub>31:0</sub> | lui rd, imm <sub>31:12</sub> * addi rd, rd, imm <sub>11:0</sub>                     | load 32-bit immediate              | rd = imm <sub>31:0</sub>              |

| mv rd, rs1                 | addi rd, rs1, 0                                                                     | move (also called "register copy") | rd = rs1                              |

| not rd, rs1                | xori rd, rs1, −1                                                                    | one's complement                   | rd = ~rs1                             |

| neg rd, rsl                | sub rd, x0, rs1                                                                     | two's complement                   | rd = -rs1                             |

| seqz rd, rs1               | sltiu rd, rsl, l                                                                    | set if = 0                         | rd = (rs1 == 0)                       |

| snez rd, rs1               | sltu rd, x0, rs1                                                                    | set if ≠ 0                         | rd = (rs1 ≠ 0)                        |

| sltz rd, rs1               | slt rd, rs1, x0                                                                     | set if < 0                         | rd = (rs1 < 0)                        |

| sgtz rd, rs1               | slt rd, x0, rs1                                                                     | set if > 0                         | rd = (rs1 > 0)                        |

| beqz rs1, label            | beq rs1, x0, label                                                                  | branch if = 0                      | if (rs1 == 0) PC = label              |

| bnez rs1, label            | bne rs1, x0, label                                                                  | branch if ≠ 0                      | if (rs1 ≠ 0) PC = label               |

| blez rs1, label            | bge x0, rs1, label                                                                  | branch if ≤ 0                      | if (rs1 ≤ 0) PC = label               |

| bgez rs1, label            | bge rs1, x0, label                                                                  | branch if $\geq 0$                 | if (rs1 ≥ 0) PC = label               |

| bltz rs1, label            | blt rs1, x0, label                                                                  | branch if < 0                      | if (rs1 < 0) PC = label               |

| bgtz rs1, label            | blt x0, rs1, label                                                                  | branch if > 0                      | if (rs1 > 0) PC = label               |

| ble rs1, rs2, label        | bge rs2, rs1, label                                                                 | branch if ≤                        | if (rs1 ≤ rs2) PC = label             |

| bgt rs1, rs2, label        | blt rs2, rs1, label                                                                 | branch if >                        | if (rs1 > rs2) PC = label             |

| bleu rs1, rs2, label       | bgeu rs2, rs1, label                                                                | branch if ≤ (unsigned)             | if (rs1 ≤ rs2) PC = label             |

| bgtu rs1, rs2, label       | bltu rs2, rs1, offset                                                               | branch if > (unsigned)             | if (rs1 > rs2) PC = label             |

| j label                    | jal x0, label                                                                       | jump                               | PC = label                            |

| jal label                  | jal ra, label                                                                       | jump and link                      | PC = label, $ra = PC + 4$             |

| jr rs1                     | jalr x0, rs1, 0                                                                     | jump register                      | PC = rs1                              |

| jalr rs1                   | jalr ra, rs1, 0                                                                     | jump and link register             | PC = rs1, $ra = PC + 4$               |

| ret                        | jalr x0, ra, 0                                                                      | return from function               | PC = ra                               |

| call label                 | jal ra, label                                                                       | call nearby function               | PC = label, ra = PC + 4               |

| call label                 | auipc ra, offset <sub>31:12</sub> * jalr ra, ra, offset <sub>11:0</sub>             | call far away function             | PC = PC + offset, ra = PC + 4         |

| la rd, symbol              | auipc rd, symbol <sub>31:12</sub> * addi rd, rd, symbol <sub>11:0</sub>             | load address of global variable    | rd = PC + symbol                      |

| l{b h w} rd, symbol        | auipc rd, $symbol_{31:12}^*$ $l\{b h w\}$ rd, $symbol_{11:0}(rd)$                   | load global variable               | rd = [PC + symbol]                    |

| s{b h w} rs2, symbol, rs1  | auipc rs1, symbol <sub>31:12</sub> * $s\{b h w\}$ rs2, symbol <sub>11:0</sub> (rs1) | store global variable              | [PC + symbol] = rs2                   |

| csrr rd, csr               | csrrs rd, csr, x0                                                                   | read CSR                           | rd = csr                              |

| csrw csr, rs1              | csrrw x0, csr, rs1                                                                  | write CSR                          | csr = rs1                             |

\* If bit 11 of the immediate / offset / symbol is 1, the upper immediate is incremented by 1. symbol and offset are the 32-bit PC-relative addresses of a label and a global variable, respectively.

#### **Table B.8 Privileged / CSR instructions**

| op            | funct3 | Type | Instruction        | Description                      |                      | Operation                               |

|---------------|--------|------|--------------------|----------------------------------|----------------------|-----------------------------------------|

| 1110011 (115) | 000    | I    | ecall              | transfer control to OS           | (imm=0)              |                                         |

| 1110011 (115) | 000    | I    | ebreak             | transfer control to debugger     | (imm=1)              |                                         |

| 1110011 (115) | 000    | I    | uret               | return from user exception       | (rs1=0,rd=0,imm=2)   | PC = uepc                               |

| 1110011 (115) | 000    | I    | sret               | return from supervisor exception | (rs1=0,rd=0,imm=258) | PC = sepc                               |

| 1110011 (115) | 000    | I    | mret               | return from machine exception    | (rs1=0,rd=0,imm=770) | PC = mepc                               |

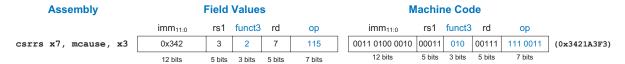

| 1110011 (115) | 001    | I    | csrrw rd,csr,rs1   | CSR read/write                   | (imm=CSR number)     | rd = csr,csr = rs1                      |

| 1110011 (115) | 010    | I    | csrrs rd,csr,rs1   | CSR read/set                     | (imm=CSR number)     | rd = csr,csr = csr   rs1                |

| 1110011 (115) | 011    | I    | csrrc rd,csr,rs1   | CSR read/clear                   | (imm=CSR number)     | rd = csr,csr = csr & ~rs1               |

| 1110011 (115) | 101    | I    | csrrwi rd,csr,uimm | CSR read/write immediate         | (imm=CSR number)     | rd = csr,csr = ZeroExt(uimm)            |

| 1110011 (115) | 110    | I    | csrrsi rd,csr,uimm | CSR read/set immediate           | (imm=CSR number)     | rd = csr,<br>csr = csr   ZeroExt(uimm)  |

| 1110011 (115) | 111    | I    | csrrci rd,csr,uimm | CSR read/clear immediate         | (imm=CSR number)     | rd = csr,<br>csr = csr & ~ZeroExt(uimm) |

## In Praise of Digital Design and Computer Architecture

#### **RISC-V Edition**

Harris and Harris have shown how to design a RISC-V processor from the gates all the way up through the microarchitecture. Their clear explanations combined with their comprehensive approach give a full picture of both digital design and the RISC-V architecture. With the exciting opportunity that students have to run large digital designs on modern FPGAs, this approach is both informative and enlightening.

David A. Patterson University of California, Berkeley

What broad fields Harris and Harris have distilled into one book! As semiconductor manufacturing matures, the importance of digital design and computer architecture will only increase. Readers will find an approachable and comprehensive treatment of both topics and will walk away with a clear understanding of the RISC-V instruction set architecture.

#### **Andrew Waterman SiFive**

There are excellent texts for teaching digital design and there are excellent texts for teaching computer hardware organization - and this textbook does both! It is also unique in its ability to connect the dots. The writing makes the RISC-V architecture understandable by building on the basics, and I have found the exercises to be a great resource across multiple courses.

#### **Roy Kravitz** Portland State University

When I first read Harris and Harris's MIPS textbook back in 2008, I thought that it was one of the best books I had ever read for teaching computer architecture. I started using it in my courses immediately. Thirteen years later, I have had the honor of reviewing this new RISC-V edition, and my opinion of their books has not changed: *Digital Design and Computer Architecture: RISC-V Edition* is an excellent book, very clear, thorough, with a high educational value, and in line with the courses that we teach in the areas of digital design and computer architecture. I look forward to using this RISC-V textbook in my courses.

Daniel Chaver Martinez University Complutense of Madrid

#### Digital Design and Computer Architecture

**RISC-V Edition**

### Digital Design and Computer Architecture

**RISC-V Edition**

Sarah L. Harris David Harris

Morgan Kaufmann is an imprint of Elsevier 50 Hampshire Street, 5th Floor, Cambridge, MA 02139, United States

Copyright © 2022 Elsevier Inc. All rights reserved.

No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying, recording, or any information storage and retrieval system, without permission in writing from the publisher. Details on how to seek permission, further information about the Publisher's permissions policies and our arrangements with organizations such as the Copyright Clearance Center and the Copyright Licensing Agency, can be found at our website: www.elsevier.com/permissions.

This book and the individual contributions contained in it are protected under copyright by the Publisher (other than as may be noted herein).

#### Notices

Knowledge and best practice in this field are constantly changing. As new research and experience broaden our understanding, changes in research methods, professional practices, or medical treatment may become necessary.

Practitioners and researchers must always rely on their own experience and knowledge in evaluating and using any information, methods, compounds, or experiments described herein. In using such information or methods they should be mindful of their own safety and the safety of others, including parties for whom they have a professional responsibility.

To the fullest extent of the law, neither the Publisher nor the authors, contributors, or editors, assume any liability for any injury and/or damage to persons or property as a matter of products liability, negligence or otherwise, or from any use or operation of any methods, products, instructions, or ideas contained in the material herein.

#### **British Library Cataloguing-in-Publication Data**

A catalogue record for this book is available from the British Library.

#### Library of Congress Cataloging-in-Publication Data

A catalog record for this book is available from the Library of Congress.

ISBN: 978-0-12-820064-3

For Information on all Morgan Kaufmann publications visit our website at https://www.elsevier.com/books-and-journals

Publisher: Katey Birtcher

Senior Acquisitions Editor: Steve Merken

Editorial Project Manager: Ruby Gammell/Andrae Akeh Senior Project Manager: Manikandan Chandrasekaran

Cover Designer: Victoria Pearson Esser

Typeset by MPS Limited, Chennai, India

Printed in the United States of America

Last digit is the print number: 9 8 7 6 5 4 3 2 1

#### **Contents**

| Prefa      | ice                                        |                                                             | xix                         |

|------------|--------------------------------------------|-------------------------------------------------------------|-----------------------------|

|            | Online<br>How to<br>Labs<br>RVfpga<br>Bugs | Supplements                                                 | xxi<br>xiii<br>xiii<br>xiii |

| Δhou       |                                            | ithors                                                      |                             |

| Abou       | t tile Au                                  | Δ                                                           | AV                          |

| Chap       | ter 1 Fr                                   | rom Zero to One                                             | . 1                         |

| 1.1<br>1.2 | The Ar<br>1.2.1<br>1.2.2                   | nme Plan t of Managing Complexity.  Abstraction  Discipline | . 2                         |

| 1.3        | 1.2.3                                      | The Three -Y's                                              |                             |

| 1.3        |                                            | gital Abstraction                                           |                             |

| 1.4        | 1.4.1                                      | er Systems                                                  |                             |

|            | 1.4.1                                      | Decimal Numbers                                             |                             |

|            | 1.4.3                                      | Binary Numbers                                              |                             |

|            | 1.4.4                                      | Bytes, Nibbles, and All That Jazz                           |                             |

|            | 1.4.5                                      | Binary Addition                                             |                             |

|            | 1.4.6                                      | Signed Binary Numbers                                       |                             |

| 1.5        |                                            | Gates                                                       |                             |

| 1.5        | 1.5.1                                      | NOT Gate                                                    |                             |

|            | 1.5.1                                      | Buffer                                                      |                             |

|            | 1.5.3                                      | AND Gate                                                    |                             |

|            | 1.5.4                                      | OR Gate                                                     |                             |

|            | 1.5.5                                      | Other Two-Input Gates                                       |                             |

|            | 1.5.6                                      | Multiple-Input Gates                                        |                             |

| 1.6        |                                            | h the Digital Abstraction                                   |                             |

| -•-        | 1.6.1                                      | Supply Voltage                                              |                             |

|            | 1.6.2                                      | Logic Levels                                                |                             |

|            | 1.6.3                                      | Noise Margins                                               |                             |

|       | 1.6.4   | DC Transfer Characteristics    | 22  |

|-------|---------|--------------------------------|-----|

|       | 1.6.5   | The Static Discipline          | 22  |

| 1.7   | CMOS    | Transistors                    | 24  |

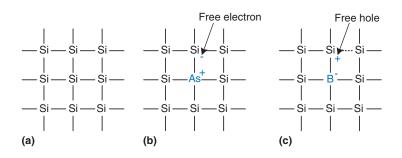

|       | 1.7.1   | Semiconductors                 | 25  |

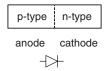

|       | 1.7.2   | Diodes                         |     |

|       | 1.7.3   | Capacitors                     |     |

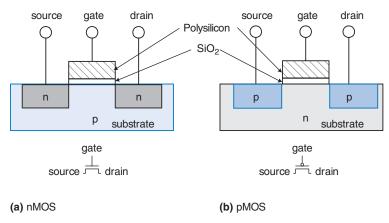

|       | 1.7.4   | nMOS and pMOS Transistors      |     |

|       | 1.7.5   | CMOS NOT Gate                  | 29  |

|       | 1.7.6   | Other CMOS Logic Gates         |     |

|       | 1.7.7   | Transmission Gates             |     |

|       | 1.7.8   | Pseudo-nMOS Logic              |     |

| 1.8   | Power   | Consumption                    | 32  |

| 1.9   | Summa   | ary and a Look Ahead           | 34  |

|       | Exercis | ses                            | 36  |

|       | Intervi | ew Questions                   | 50  |

| Chan  | tor 2 C | ombinational Logic Design      | 5.2 |

| Ullap |         |                                |     |

| 2.1   | Introdu | uction                         | 53  |

| 2.2   | Boolea  | n Equations                    | 56  |

|       | 2.2.1   | Terminology                    | 56  |

|       | 2.2.2   | Sum-of-Products Form           | 56  |

|       | 2.2.3   | Product-of-Sums Form           | 58  |

| 2.3   | Boolea  | n Algebra                      | 58  |

|       | 2.3.1   | Axioms                         | 59  |

|       | 2.3.2   | Theorems of One Variable       | 59  |

|       | 2.3.3   | Theorems of Several Variables  | 60  |

|       | 2.3.4   | The Truth Behind It All        | 62  |

|       | 2.3.5   | Simplifying Equations          |     |

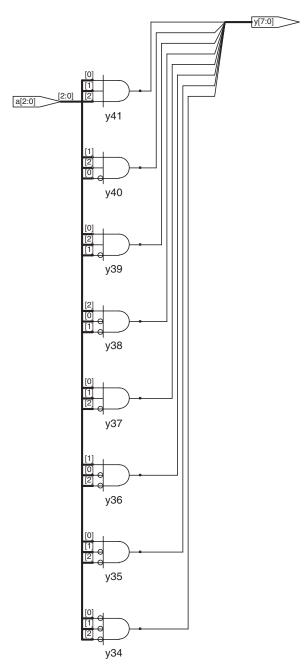

| 2.4   |         | Logic to Gates                 |     |

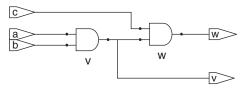

| 2.5   |         | evel Combinational Logic       |     |

|       | 2.5.1   | Hardware Reduction             |     |

|       | 2.5.2   | Bubble Pushing                 |     |

| 2.6   | X's and | d Z's, Oh My                   |     |

|       | 2.6.1   | Illegal Value: X               |     |

|       | 2.6.2   | Floating Value: Z              |     |

| 2.7   |         | ıgh Maps                       |     |

|       | 2.7.1   | Circular Thinking              |     |

|       | 2.7.2   | Logic Minimization with K-Maps |     |

|       | 2.7.3   | Don't Cares                    |     |

|       | 2.7.4   | The Big Picture                |     |

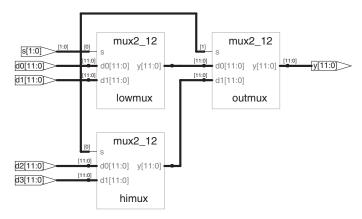

| 2.8   |         | national Building Blocks       |     |

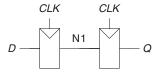

|       | 2.8.1   | Multiplexers                   |     |

|       | 2.8.2   | Decoders                       | 84  |

| 2.9  | Timing                 |                                      | 86  |  |  |  |  |

|------|------------------------|--------------------------------------|-----|--|--|--|--|

|      | 2.9.1                  | Propagation and Contamination Delay  |     |  |  |  |  |

|      | 2.9.2                  | Glitches                             |     |  |  |  |  |

| 2.10 |                        | ry                                   |     |  |  |  |  |

|      |                        | es                                   |     |  |  |  |  |

|      |                        | w Questions                          |     |  |  |  |  |

| Chon | tor 2 Co               | guential Legie Decign                | 107 |  |  |  |  |

| опар |                        | equential Logic Design               | 107 |  |  |  |  |

| 3.1  | Introdu                | ction                                | 107 |  |  |  |  |

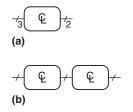

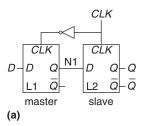

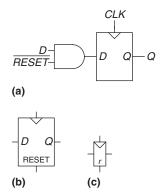

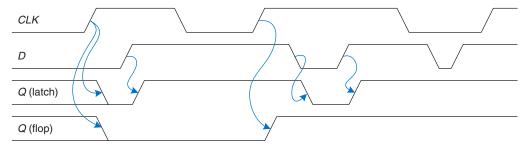

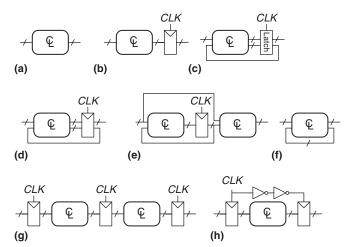

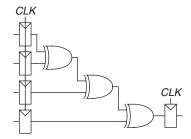

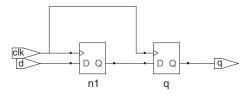

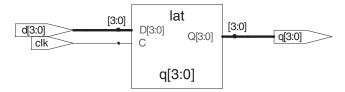

| 3.2  | Latches                | and Flip-Flops                       | 107 |  |  |  |  |

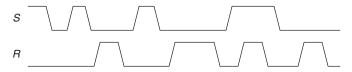

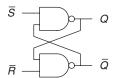

|      | 3.2.1                  | <i>SR Latch</i>                      | 109 |  |  |  |  |

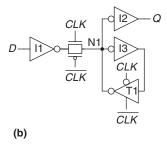

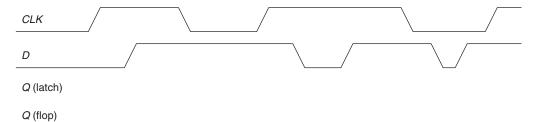

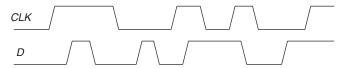

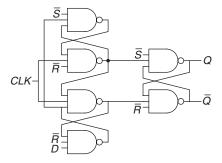

|      | 3.2.2                  | D Latch                              | 111 |  |  |  |  |

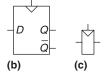

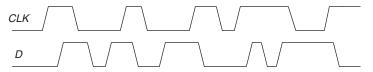

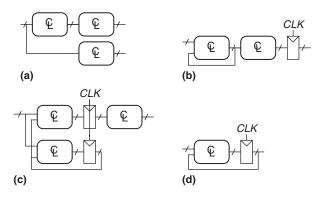

|      | 3.2.3                  | D Flip-Flop                          | 112 |  |  |  |  |

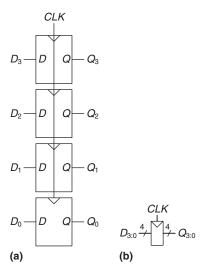

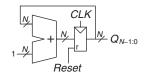

|      | 3.2.4                  | Register                             | 112 |  |  |  |  |

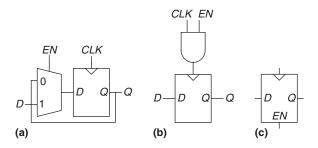

|      | 3.2.5                  | Enabled Flip-Flop                    | 113 |  |  |  |  |

|      | 3.2.6                  | Resettable Flip-Flop                 | 114 |  |  |  |  |

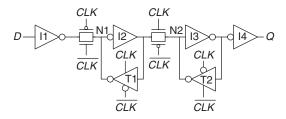

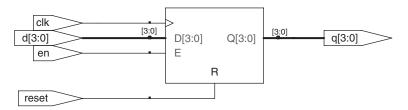

|      | 3.2.7                  | Transistor-Level Latch and Flip-Flop |     |  |  |  |  |

|      |                        | Designs                              | 114 |  |  |  |  |

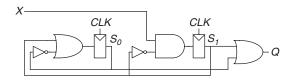

|      | 3.2.8                  | Putting It All Together              |     |  |  |  |  |

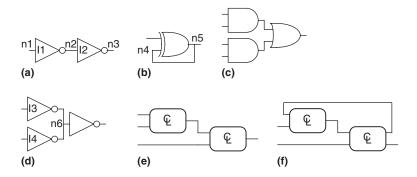

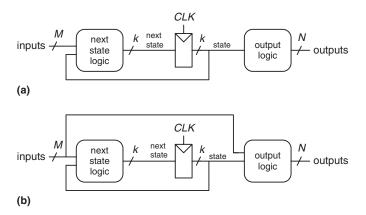

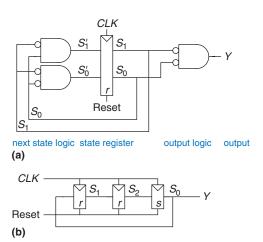

| 3.3  | Synchro                | onous Logic Design                   |     |  |  |  |  |

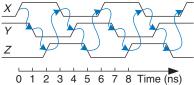

|      | 3.3.1                  | Some Problematic Circuits            | 117 |  |  |  |  |

|      | 3.3.2                  | Synchronous Sequential Circuits      | 118 |  |  |  |  |

|      | 3.3.3                  | Synchronous and Asynchronous         |     |  |  |  |  |

|      |                        | Circuits                             | 120 |  |  |  |  |

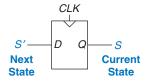

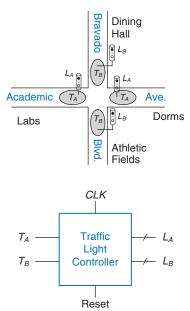

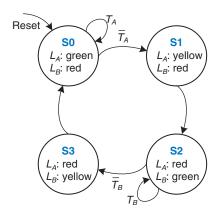

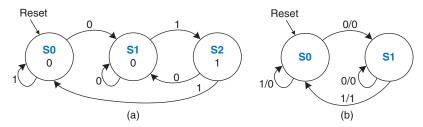

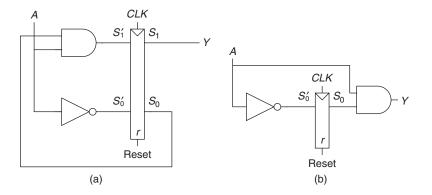

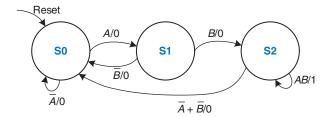

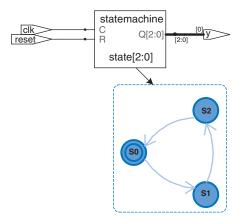

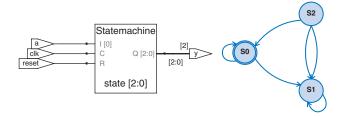

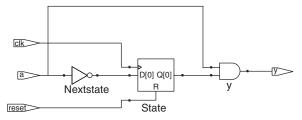

| 3.4  | Finite State Machines. |                                      |     |  |  |  |  |

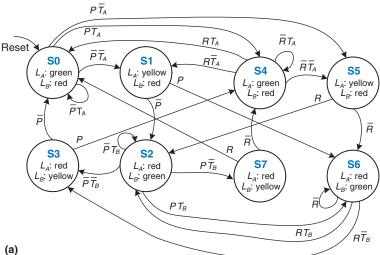

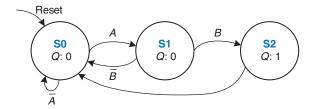

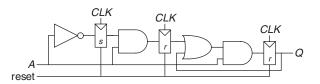

|      | 3.4.1                  | FSM Design Example                   | 121 |  |  |  |  |

|      | 3.4.2                  | State Encodings                      | 127 |  |  |  |  |

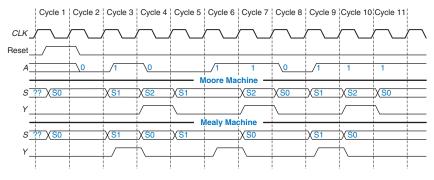

|      | 3.4.3                  | Moore and Mealy Machines             | 130 |  |  |  |  |

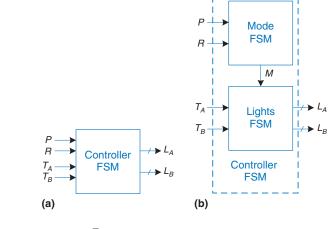

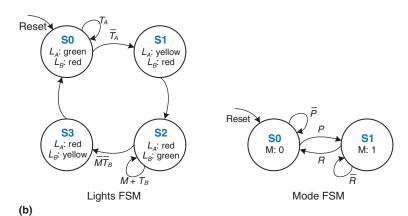

|      | 3.4.4                  | Factoring State Machines             | 132 |  |  |  |  |

|      | 3.4.5                  | Deriving an FSM from a Schematic     | 135 |  |  |  |  |

|      | 3.4.6                  | FSM Review                           | 138 |  |  |  |  |

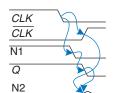

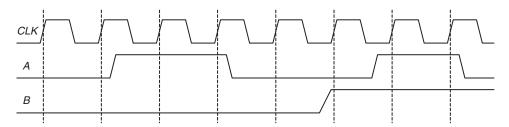

| 3.5  | Timing                 | of Sequential Logic                  | 139 |  |  |  |  |

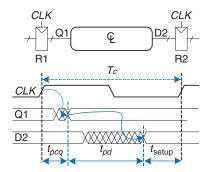

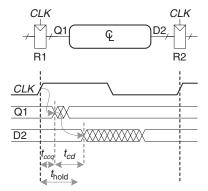

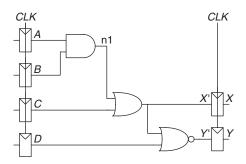

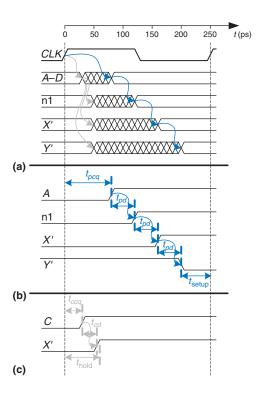

|      | 3.5.1                  | The Dynamic Discipline               | 140 |  |  |  |  |

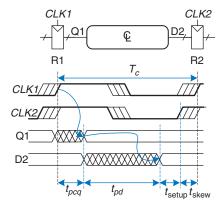

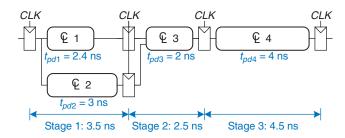

|      | 3.5.2                  | System Timing                        | 140 |  |  |  |  |

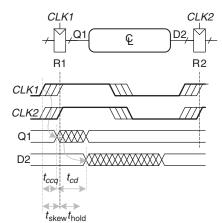

|      | 3.5.3                  | Clock Skew                           | 146 |  |  |  |  |

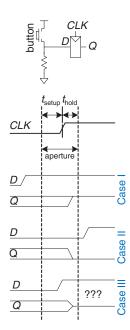

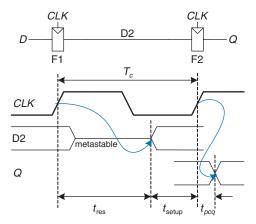

|      | 3.5.4                  | Metastability                        | 149 |  |  |  |  |

|      | 3.5.5                  | Synchronizers                        | 150 |  |  |  |  |

|      | 3.5.6                  | Derivation of Resolution Time        | 152 |  |  |  |  |

| 3.6  |                        | ism                                  | 155 |  |  |  |  |

| 3.7  |                        | ry                                   | 159 |  |  |  |  |

|      |                        | es                                   | 160 |  |  |  |  |

|      |                        | w Ouestions                          | 169 |  |  |  |  |

xii

| Chap | ter 4 Ha | ardware Description Languages        | 171 |

|------|----------|--------------------------------------|-----|

| 4.1  | Introdu  | action                               | 171 |

|      | 4.1.1    | Modules                              |     |

|      | 4.1.2    | Language Origins                     |     |

|      | 4.1.3    | Simulation and Synthesis             |     |

| 4.2  |          | national Logic                       |     |

|      | 4.2.1    | Bitwise Operators                    |     |

|      | 4.2.2    | Comments and White Space             |     |

|      | 4.2.3    | Reduction Operators                  |     |

|      | 4.2.4    | Conditional Assignment               |     |

|      | 4.2.5    | Internal Variables                   | 180 |

|      | 4.2.6    | Precedence                           | 182 |

|      | 4.2.7    | Numbers                              | 183 |

|      | 4.2.8    | <i>Z's and X's</i>                   | 184 |

|      | 4.2.9    | Bit Swizzling                        | 186 |

|      | 4.2.10   | Delays                               | 186 |

| 4.3  | Structu  | ral Modeling                         | 188 |

| 4.4  |          | tial Logic                           | 191 |

|      | 4.4.1    | Registers                            | 191 |

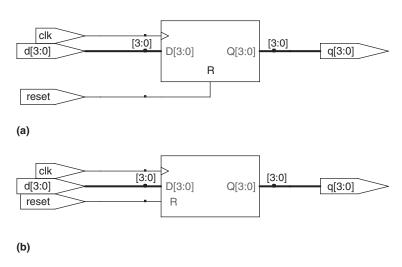

|      | 4.4.2    | Resettable Registers                 | 192 |

|      | 4.4.3    | Enabled Registers                    |     |

|      | 4.4.4    | Multiple Registers                   | 195 |

|      | 4.4.5    | Latches                              | 196 |

| 4.5  | More C   | Combinational Logic                  | 196 |

|      | 4.5.1    | Case Statements                      |     |

|      | 4.5.2    | If Statements                        | 200 |

|      | 4.5.3    | Truth Tables with Don't Cares        | 203 |

|      | 4.5.4    | Blocking and Nonblocking Assignments | 203 |

| 4.6  | Finite S | tate Machines                        | 207 |

| 4.7  | Data Ty  | ypes                                 | 211 |

|      | 4.7.1    | SystemVerilog                        | 212 |

|      | 4.7.2    | VHDL                                 | 213 |

| 4.8  |          | terized Modules                      |     |

| 4.9  | Testben  | nches                                | 218 |

| 4.10 |          | ry                                   |     |

|      | Exercis  | es                                   | 224 |

|      | Intervie | ew Questions                         | 235 |

| Chap | ter 5 Di | gital Building Blocks                | 237 |

| 5.1  | Introdu  | action                               | 237 |

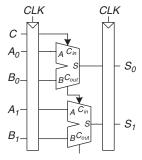

| 5.2  |          | etic Circuits                        |     |

| J.Z  | 5.2.1    | Addition                             |     |

|      |          | Subtraction                          |     |

|      | J.4.4    | Subtraction                          | 477 |

**CONTENTS** xiii

|       | 5.2.3    | Comparators                                | 245 |

|-------|----------|--------------------------------------------|-----|

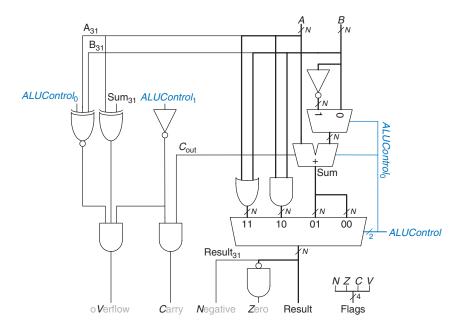

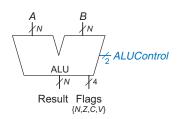

|       | 5.2.4    | ALU                                        |     |

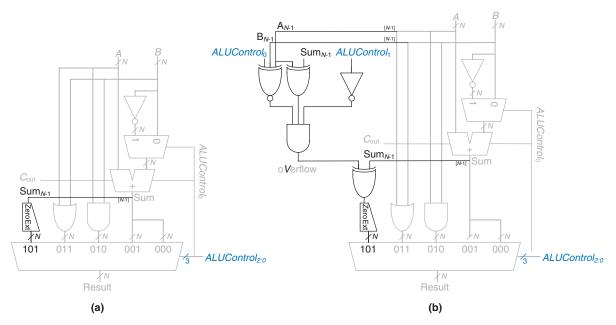

|       | 5.2.5    | Shifters and Rotators                      | 251 |

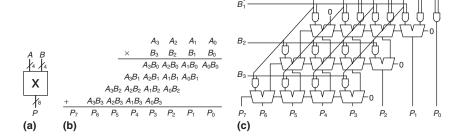

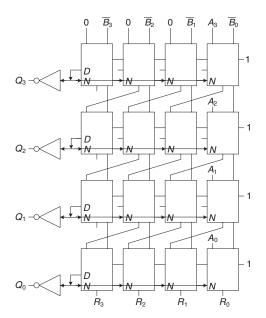

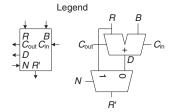

|       | 5.2.6    | Multiplication                             |     |

|       | 5.2.7    | Division                                   |     |

|       | 5.2.8    | Further Reading                            | 255 |

| 5.3   | Numb     | er Systems                                 | 256 |

|       | 5.3.1    | Fixed-Point Number Systems                 |     |

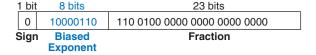

|       | 5.3.2    | Floating-Point Number Systems              |     |

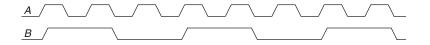

| 5.4   | Sequen   | ntial Building Blocks                      |     |

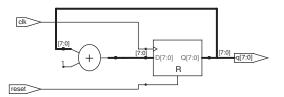

|       | 5.4.1    | Counters                                   |     |

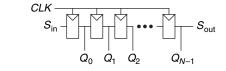

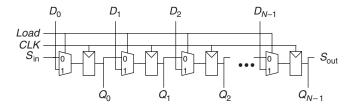

|       | 5.4.2    | Shift Registers                            |     |

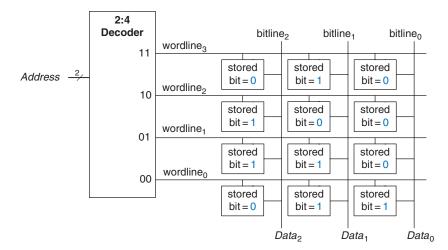

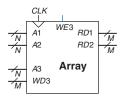

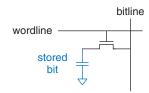

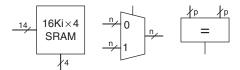

| 5.5   | Memo     | ry Arrays                                  |     |

|       | 5.5.1    | Overview                                   |     |

|       | 5.5.2    | Dynamic Random Access Memory (DRAM)        |     |

|       | 5.5.3    | Static Random Access Memory (SRAM)         |     |

|       | 5.5.4    | Area and Delay                             |     |

|       | 5.5.5    | Register Files                             |     |

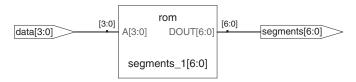

|       | 5.5.6    | Read Only Memory (ROM)                     |     |

|       | 5.5.7    | Logic Using Memory Arrays                  |     |

|       | 5.5.8    | Memory HDL                                 |     |

| 5.6   | Logic A  | Arrays                                     |     |

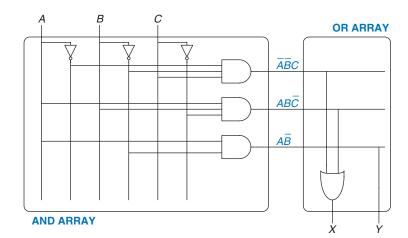

|       | 5.6.1    | Programmable Logic Array (PLA)             |     |

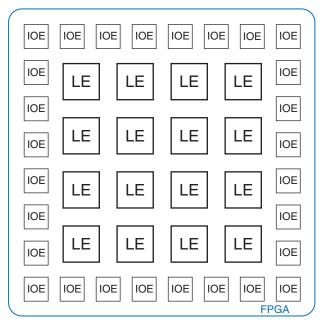

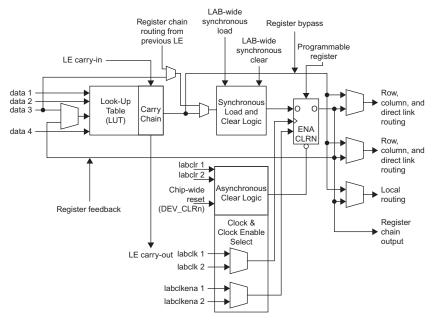

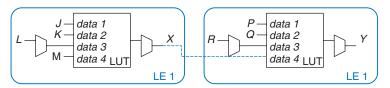

|       | 5.6.2    | Field Programmable Gate Array (FPGA)       |     |

|       | 5.6.3    | Array Implementations                      |     |

| 5.7   | Summa    | ary                                        |     |

|       | Exercis  | ses                                        | 285 |

|       |          | ew Questions                               |     |

|       |          | •                                          |     |

| Char  | stor G A | rchitecture                                | 299 |

| Ullap | ACI O A  | ioniteoture                                | ムフラ |

| 6.1   | Introdu  | uction                                     | 299 |

| 6.2   | Assem    | bly Language                               | 300 |

|       | 6.2.1    | Instructions                               | 301 |

|       | 6.2.2    | Operands: Registers, Memory, and Constants |     |

| 6.3   | Progra   | mming                                      | 308 |

|       | 6.3.1    | Program Flow                               |     |

|       | 6.3.2    | Logical, Shift, and Multiply Instructions  | 308 |

|       | 6.3.3    | Branching                                  | 311 |

|       | 6.3.4    | Conditional Statements                     | 313 |

|       | 6.3.5    | Getting Loopy                              | 315 |

|       | 6.3.6    | Arrays                                     |     |

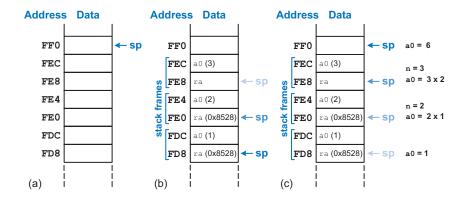

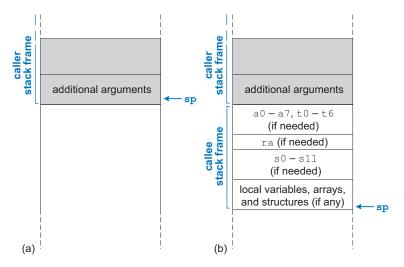

|       | 6.3.7    | Function Calls                             | 320 |

|       | 638      | Pandoinstructions                          | 330 |

xiv **CONTENTS**

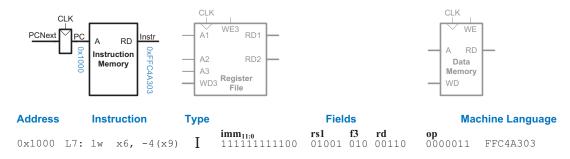

| 6.4  | Machin  | ne Language                                 | 332        |

|------|---------|---------------------------------------------|------------|

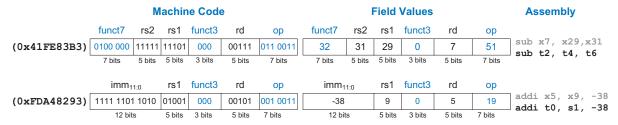

|      | 6.4.1   | R-Type Instructions                         |            |

|      | 6.4.2   | l-Type Instructions                         |            |

|      | 6.4.3   | S/B-Type Instructions                       |            |

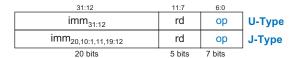

|      | 6.4.4   | U/J-Type Instructions                       |            |

|      | 6.4.5   | Immediate Encodings                         |            |

|      | 6.4.6   | Addressing Modes                            |            |

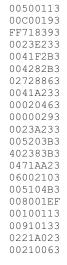

|      | 6.4.7   | Interpreting Machine Language Code          |            |

|      | 6.4.8   | The Power of the Stored Program             |            |

| 6.5  | Lights, | Camera, Action: Compiling, Assembling,      |            |

|      | and Lo  | pading                                      | 344        |

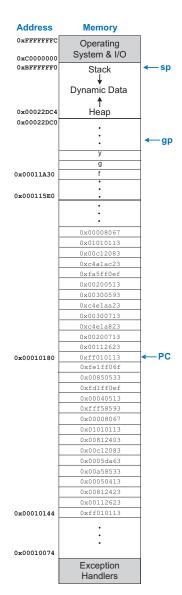

|      | 6.5.1   | The Memory Map                              |            |

|      | 6.5.2   | Assembler Directives                        |            |

|      | 6.5.3   | Compiling                                   | 348        |

|      | 6.5.4   | Assembling                                  |            |

|      | 6.5.5   | Linking                                     |            |

|      | 6.5.6   | Loading                                     |            |

| 6.6  | Odds a  | and Ends                                    |            |

|      | 6.6.1   | Endianness                                  | 355        |

|      | 6.6.2   | Exceptions                                  | 356        |

|      | 6.6.3   | Signed and Unsigned Instructions            |            |

|      | 6.6.4   | Floating-Point Instructions                 | 361        |

|      | 6.6.5   | Compressed Instructions                     | 362        |

| 6.7  | Evoluti | ion of the RISC-V Architecture              | 363        |

|      | 6.7.1   | RISC-V Base Instruction Sets and Extensions | 364        |

|      | 6.7.2   | Comparison of RISC-V and MIPS Architectures | 365        |

|      | 6.7.3   | Comparison of RISC-V and ARM Architectures  | 365        |

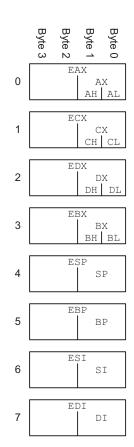

| 6.8  | Anothe  | er Perspective: x86 Architecture            | 366        |

|      | 6.8.1   | x86 Registers                               |            |

|      | 6.8.2   | <i>x</i> 86 Operands                        | 367        |

|      | 6.8.3   | Status Flags                                | 369        |

|      | 6.8.4   | x86 Instructions                            | 369        |

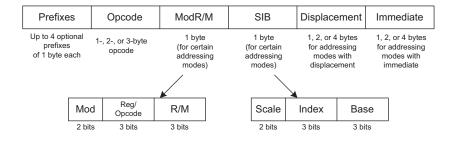

|      | 6.8.5   | x86 Instruction Encoding                    | 371        |

|      | 6.8.6   | Other x86 Peculiarities                     | 372        |

|      | 6.8.7   | The Big Picture                             | 373        |

| 6.9  | Summa   | ary                                         | 374        |

|      |         | ses                                         |            |

|      | Intervi | ew Questions                                | 390        |

| Chan | ter 7 M | licroarchitecture                           | 393        |

|      |         | uction .                                    |            |

| 7.1  |         |                                             |            |

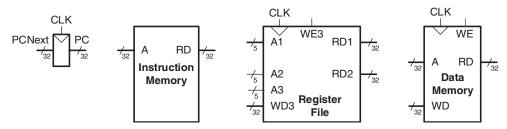

|      | 7.1.1   | Architectural State and Instruction Set     |            |

|      | 7.1.2   | Design Process                              | 394<br>396 |

|      | / 1 3   | IVI1CT()ATCHITPCTIATPS                      | 376        |

**CONTENTS** XV

| 7.2          | Perform  | nance Analysis                  | 397 |

|--------------|----------|---------------------------------|-----|

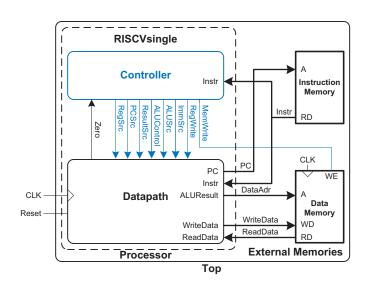

| 7.3          |          | Cycle Processor                 | 398 |

|              | 7.3.1    | Sample Program                  |     |

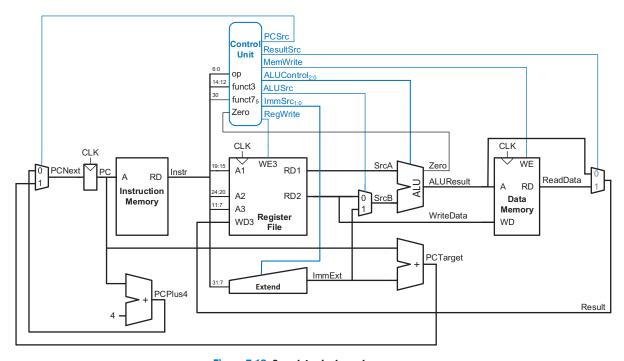

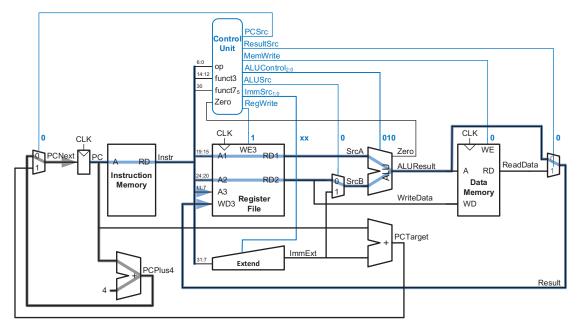

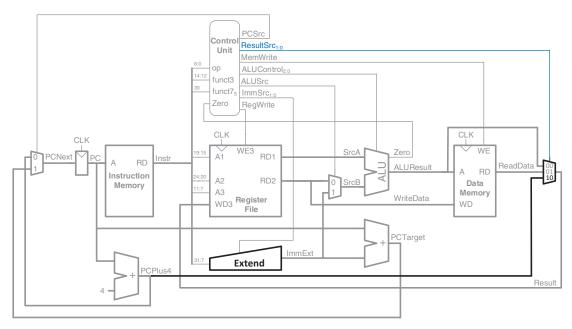

|              | 7.3.2    | Single-Cycle Datapath           | 399 |

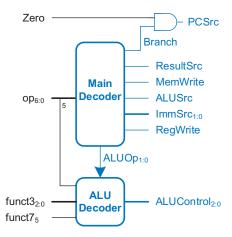

|              | 7.3.3    | Single-Cycle Control            | 407 |

|              | 7.3.4    | More Instructions               | 410 |

|              | 7.3.5    | Performance Analysis            | 412 |

| 7.4          |          | vele Processor                  | 415 |

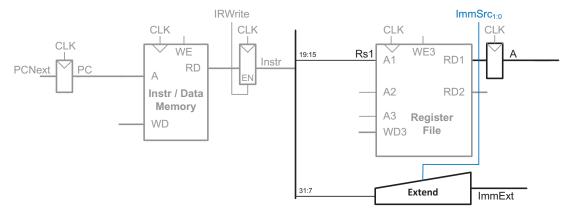

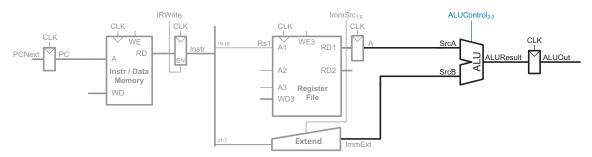

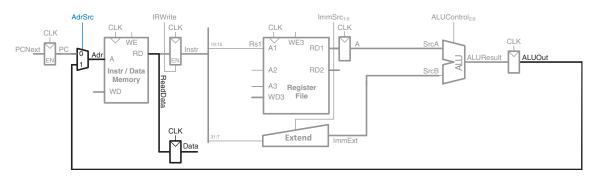

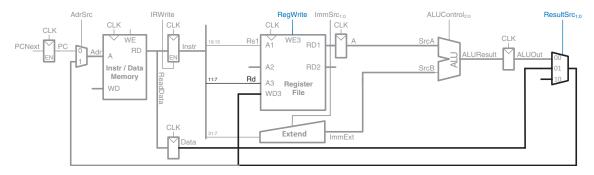

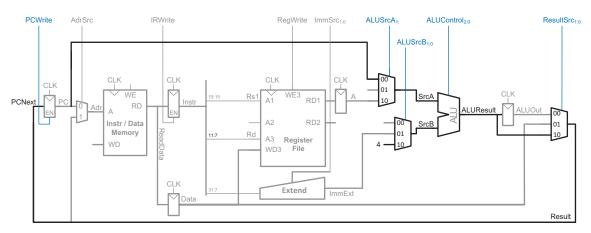

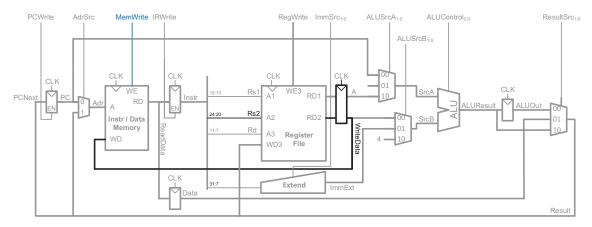

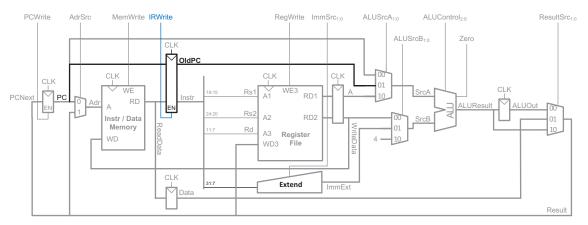

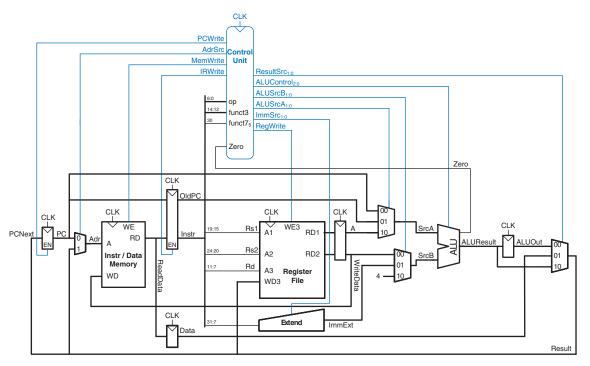

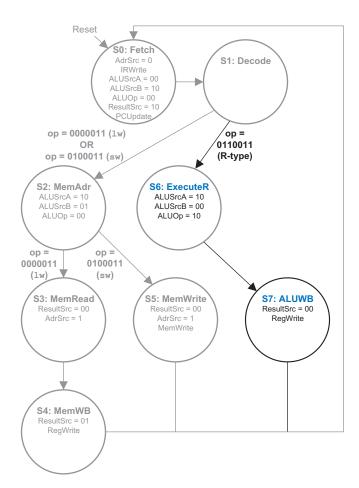

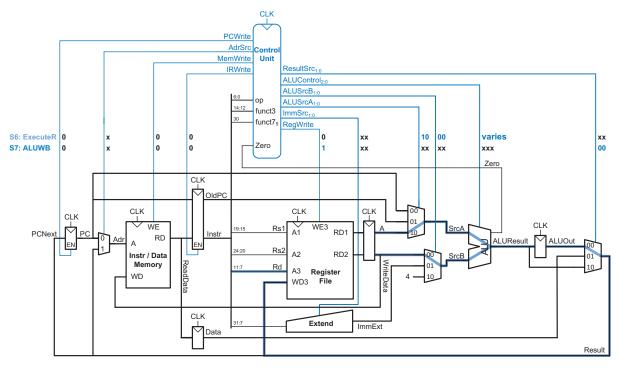

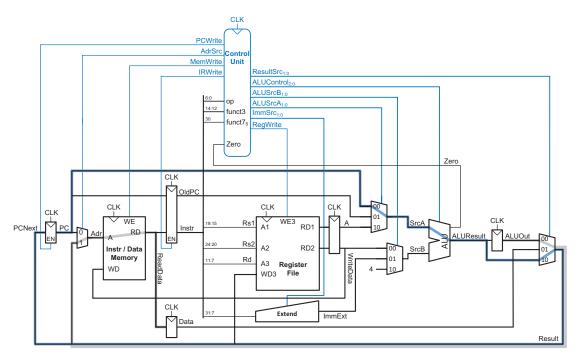

|              | 7.4.1    | Multicycle Datapath             | 416 |

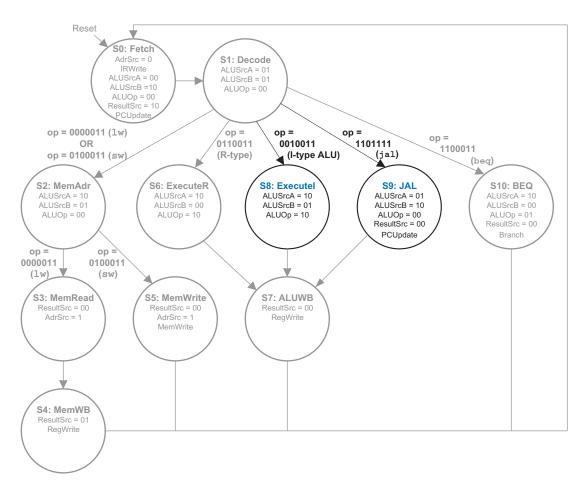

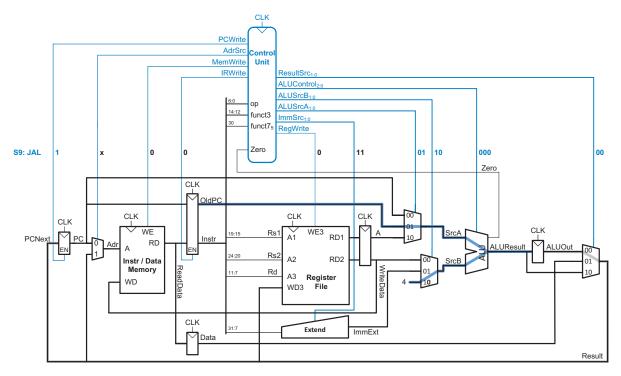

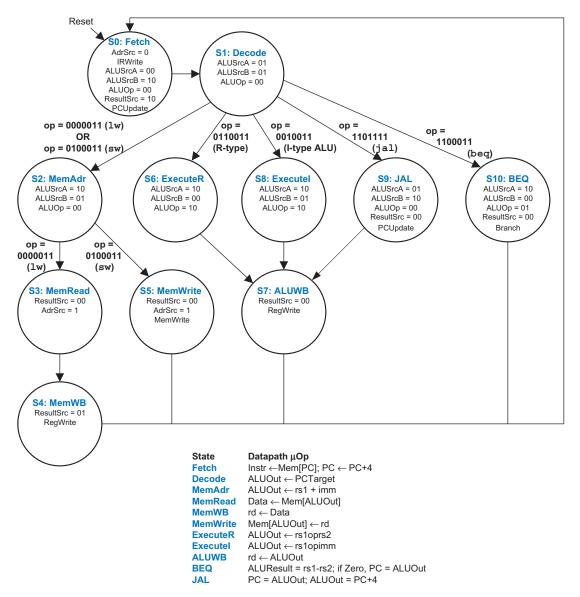

|              | 7.4.2    | Multicycle Control              | 422 |

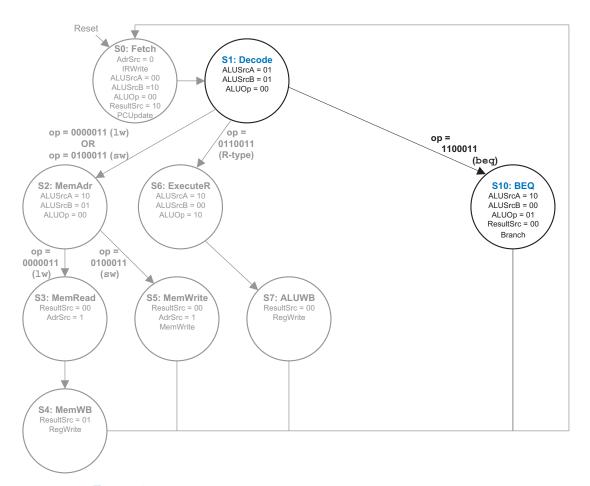

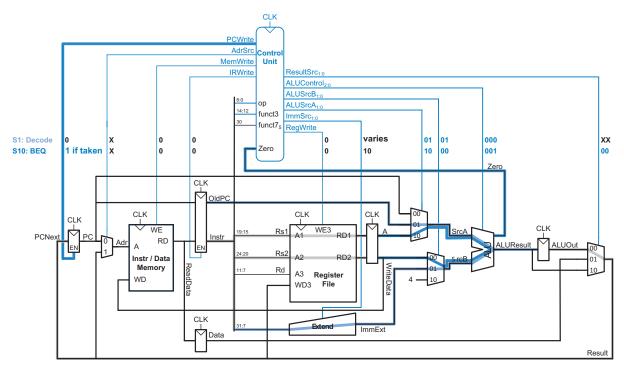

|              | 7.4.3    | More Instructions               | 432 |

|              | 7.4.4    | Performance Analysis            | 435 |

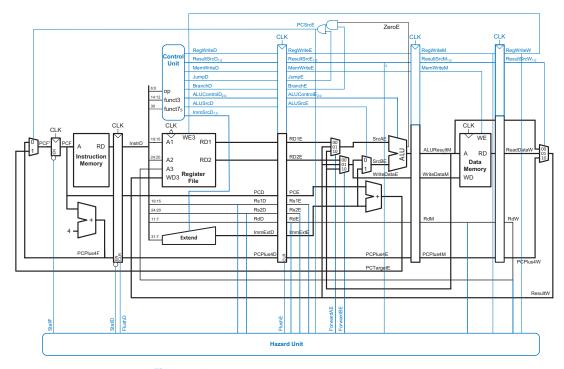

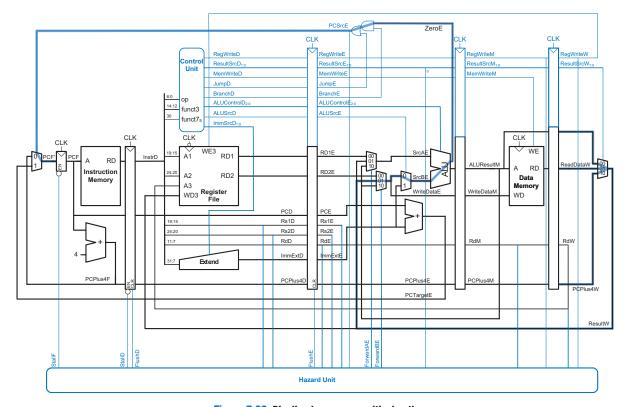

| 7.5          | Pipeline | ed Processor                    | 439 |

| , •0         | 7.5.1    | Pipelined Datapath              | 441 |

|              | 7.5.2    | Pipelined Control               | 443 |

|              | 7.5.3    | Hazards                         | 443 |

|              | 7.5.4    | Performance Analysis            | 454 |

| 7.6          |          | epresentation                   | 456 |

| , <b>.</b> 0 | 7.6.1    | Single-Cycle Processor          | 457 |

|              | 7.6.2    | Generic Building Blocks         | 461 |

|              | 7.6.3    | Testbench                       | 464 |

| 7.7          |          | red Microarchitecture           | 468 |

| , •,         | 7.7.1    | Deep Pipelines                  | 468 |

|              | 7.7.2    | Micro-Operations                | 469 |

|              | 7.7.3    | Branch Prediction               | 470 |

|              | 7.7.4    | Superscalar Processors          | 472 |

|              | 7.7.5    | Out-of-Order Processor.         | 473 |

|              | 7.7.6    | Register Renaming               | 476 |

|              | 7.7.7    | Multithreading                  | 478 |

|              | 7.7.8    | Multiprocessors                 | 479 |

| 7.8          |          | orld Perspective: Evolution of  | 1// |

| 7.0          |          | Microarchitecture               | 482 |

| 7.9          |          | ry                              | 486 |

| 1.2          |          | es                              | 488 |

|              |          | w Questions                     | 497 |

|              |          |                                 | 177 |

| Chap         | ter 8 M  | emory Systems                   | 499 |

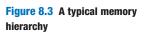

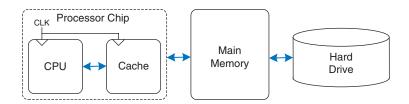

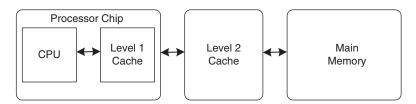

| 8.1          | Introdu  | ction                           | 499 |

| 8.2          |          | y System Performance Analysis   | 503 |

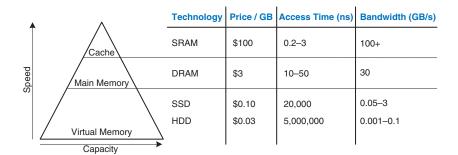

| 8.3          |          |                                 | 505 |

|              | 8.3.1    | What Data is Held in the Cache? | 505 |

|              | 8.3.2    | How is Data Found?              | 506 |

|              | 8.3.3    | What Data is Replaced?          |     |

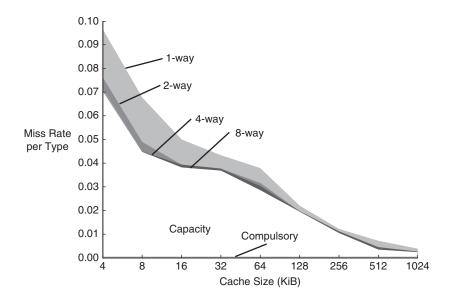

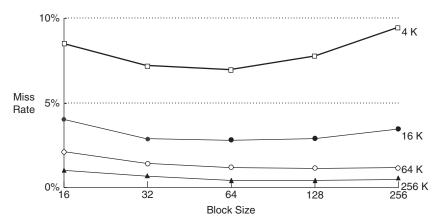

|              | 8.3.4    | Advanced Cache Design           |     |

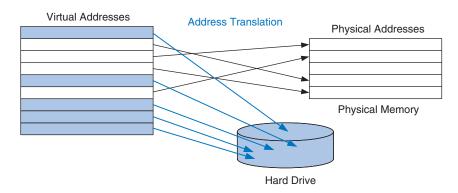

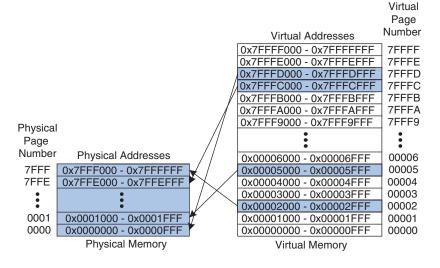

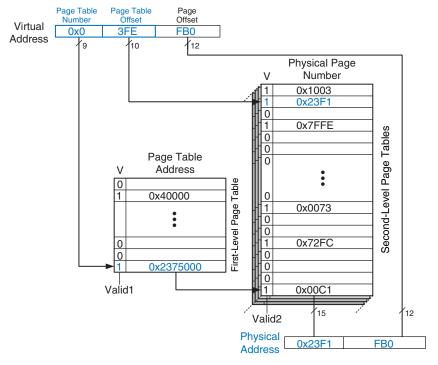

| 8.4  | Virtual Memory 51                                | 9          |

|------|--------------------------------------------------|------------|

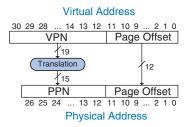

|      | 8.4.1 <i>Address Translation</i>                 | 22         |

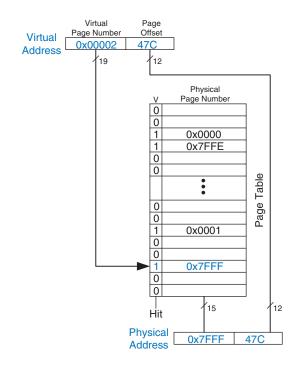

|      | 8.4.2 <i>The Page Table</i>                      | 23         |

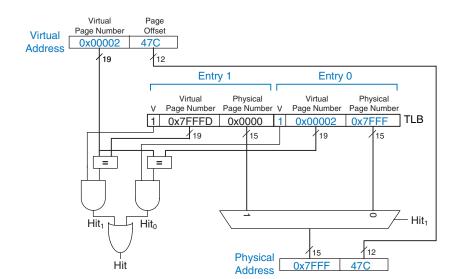

|      | 8.4.3 The Translation Lookaside Buffer 52        | 25         |

|      | 8.4.4 <i>Memory Protection</i>                   | 26         |

|      | 8.4.5 Replacement Policies                       | 27         |

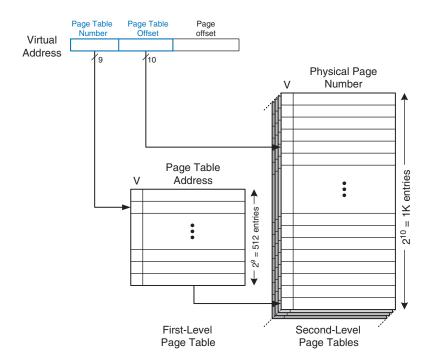

|      | 8.4.6 Multilevel Page Tables 52                  |            |

| 8.5  | Summary                                          |            |

|      | Epilogue                                         | 30         |

|      | Exercises                                        | 32         |

|      | Interview Questions                              | 1          |

| Chap | oter 9 Embedded I/O Systems                      | ł2         |

| 9.1  | Introduction                                     | ł2         |

| Chap | oter 9 is available as an online supplement542.6 | <u>.</u> 1 |

| 9.1  | Introduction                                     | 1 د        |

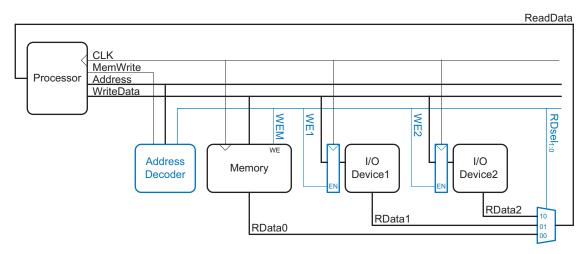

| 9.2  | Memory-Mapped I/O542.6                           |            |

| 9.3  | Embedded I/O Systems                             | 3          |

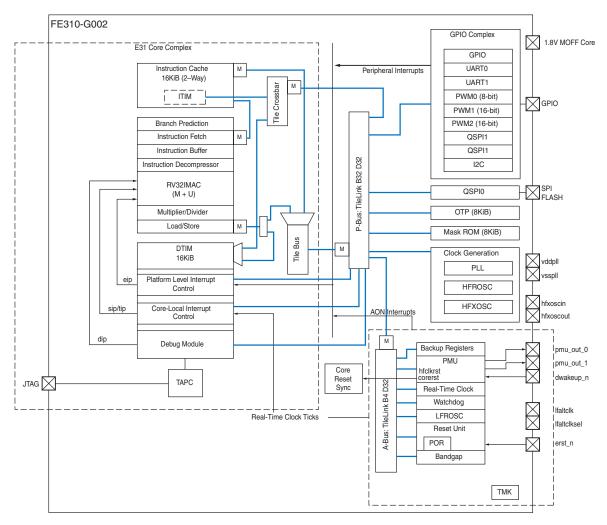

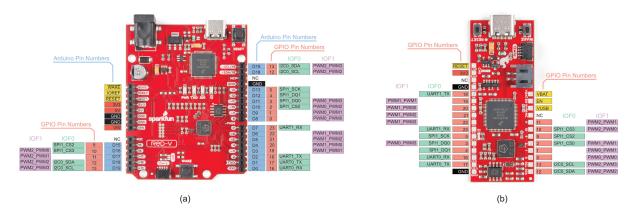

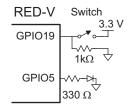

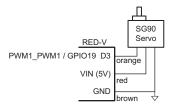

|      | 9.3.1 RED-V Board                                |            |

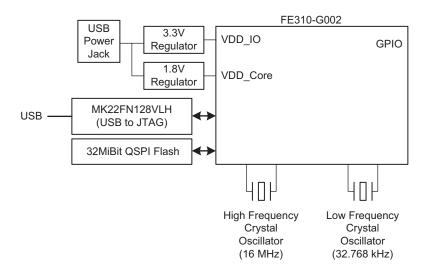

|      | 9.3.2 FE310-G002 System-on-Chip                  |            |

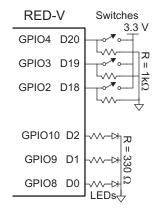

|      | 9.3.3 General-Purpose Digital I/O                |            |

|      | 9.3.4 <i>Device Drivers</i>                      |            |

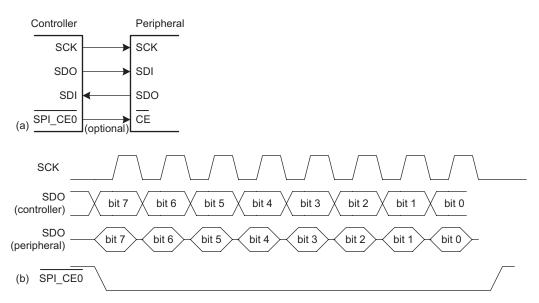

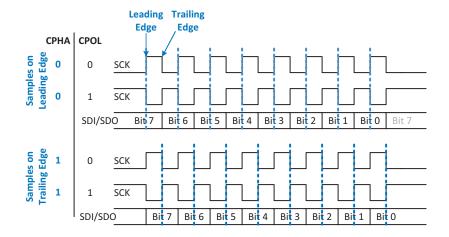

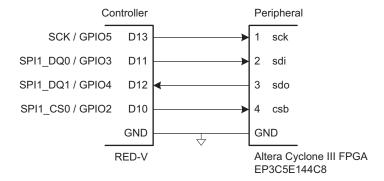

|      | 9.3.5 <i>Serial I/O</i>                          |            |

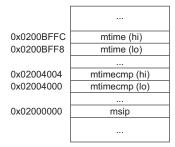

|      | 9.3.6 <i>Timers</i>                              | 29         |

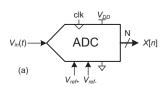

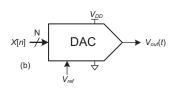

|      | 9.3.7 <i>Analog I/O</i>                          | 30         |

|      | 9.3.8 <i>Interrupts</i>                          | 39         |

| 9.4  | Other Microcontroller Peripherals                |            |

|      | 9.4.1 <i>Character LCDs</i>                      | 13         |

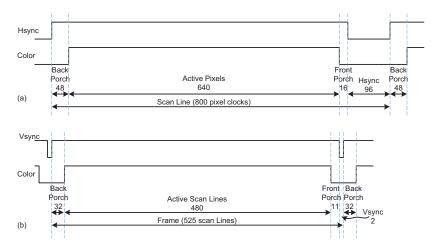

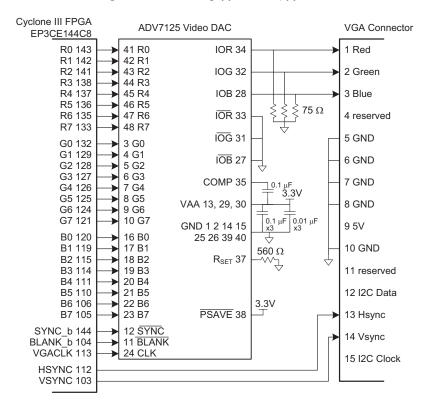

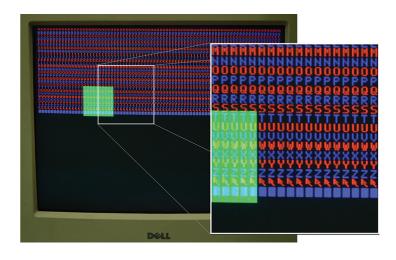

|      | 9.4.2 <i>VGA Monitor</i>                         |            |

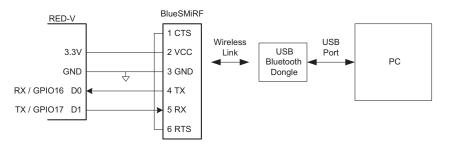

|      | 9.4.3 Bluetooth Wireless Communication 542.e5    |            |

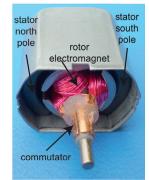

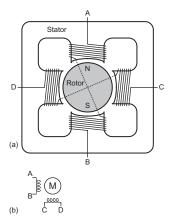

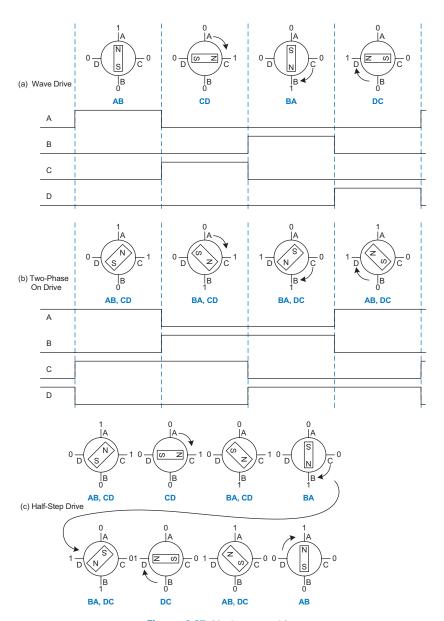

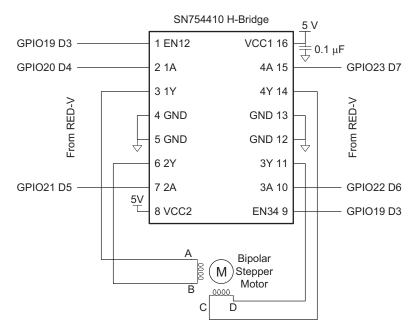

|      | 9.4.4 <i>Motor Control</i>                       | 54         |

| 9.5  | Summary                                          | 54         |

| Appe | endix A Digital System Implementation 54         | 13         |

| A.1  | Introduction                                     | 13         |

| Appe | endix A is available as an online supplement     | :1         |

| A.1  | Introduction                                     |            |

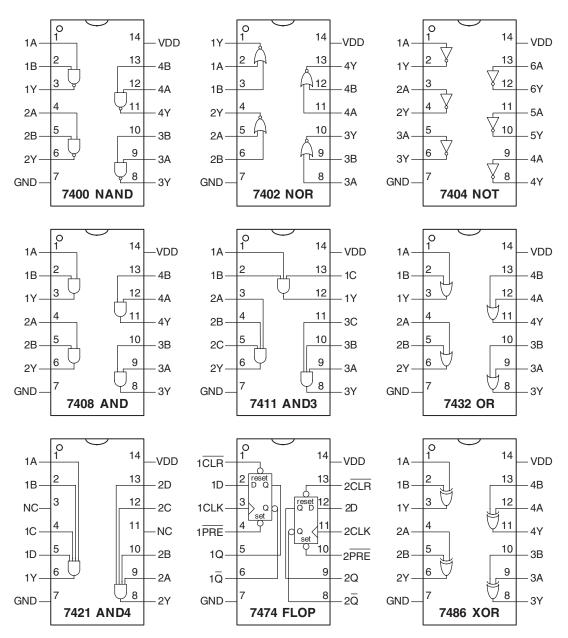

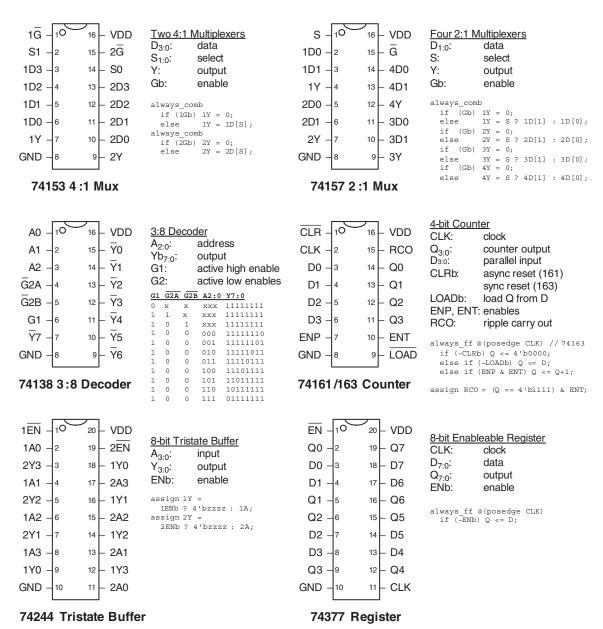

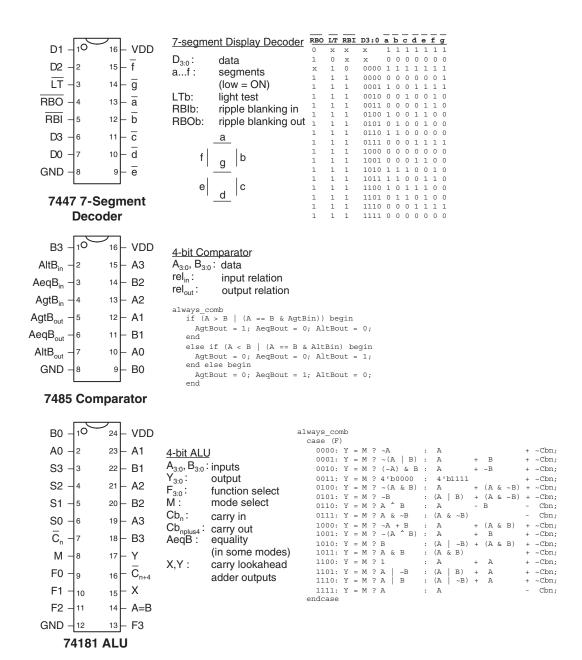

| A.2  | 74xx Logic                                       |            |

|      | A.2.1 Logic Gates                                | 2          |

|      | A.2.2 Other Functions 543.6                      | 2          |

CONTENTS xvii

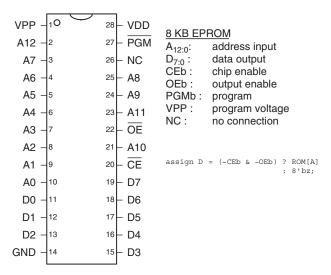

| A.3  | Progra | mmable Logic                             | 543.e2  |

|------|--------|------------------------------------------|---------|

|      | A.3.1  | PROMs                                    | 543.e2  |

|      | A.3.2  | <i>PLAs</i>                              | 543.e6  |

|      | A.3.3  | FPGAs                                    | 543.e7  |

| A.4  | Applic | ation-Specific Integrated Circuits       | 543.e9  |

| A.5  | Datash | ieets                                    | 543.e9  |

| A.6  |        | Families                                 |         |

| A.7  | Switch | es and Light-Emitting Diodes             | 543.e17 |

|      | A.7.1  | Switches                                 |         |

|      | A.7.2  | LEDs                                     | 543.e18 |

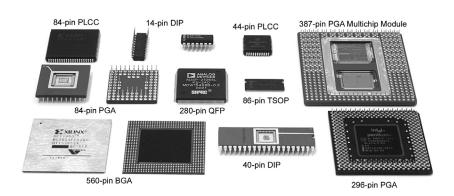

| A.8  | Packag | ging and Assembly                        | 543.e19 |

|      | A.8.1  | Packages                                 | 543.e19 |

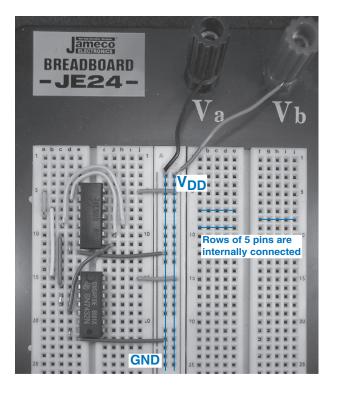

|      | A.8.2  | Breadboards                              | 543.e20 |

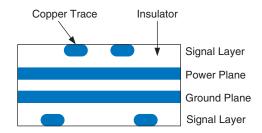

|      | A.8.3  | Printed Circuit Boards                   | 543.e20 |

|      | A.8.4  | Putting It All Together                  | 543.e23 |

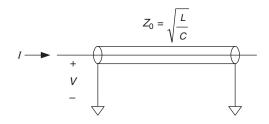

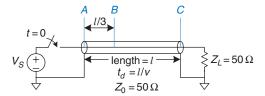

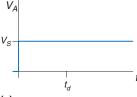

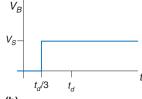

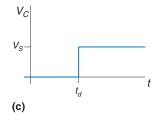

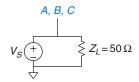

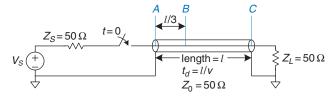

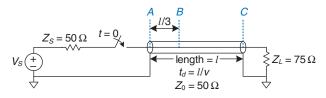

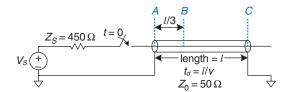

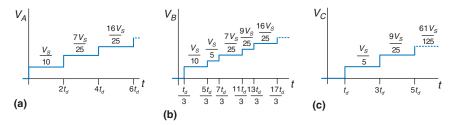

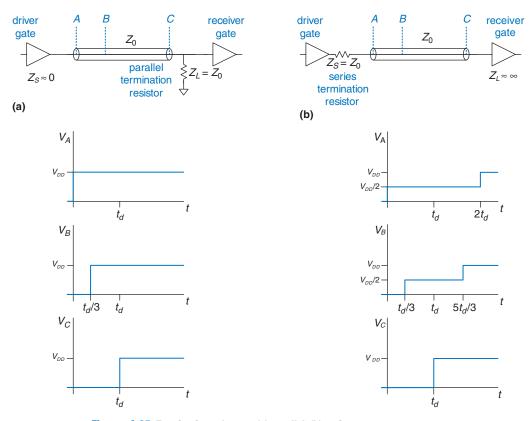

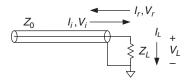

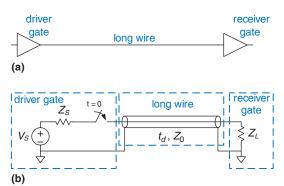

| A.9  | Transn | nission Lines                            | 543.e23 |

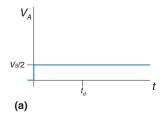

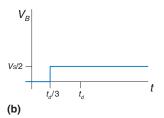

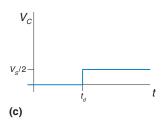

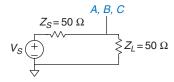

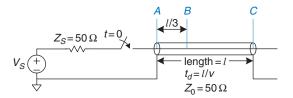

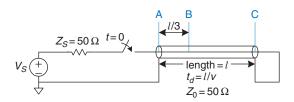

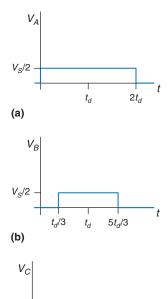

|      | A.9.1  | Matched Termination                      | 543.e24 |

|      | A.9.2  | Open Termination                         | 543.e26 |

|      | A.9.3  | Short Termination                        | 543.e27 |

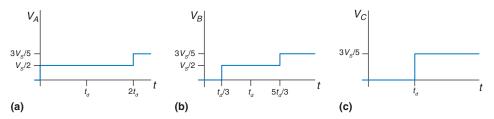

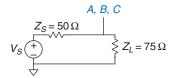

|      | A.9.4  | Mismatched Termination                   | 543.e27 |

|      | A.9.5  | When to Use Transmission Line Models     | 543.e30 |

|      | A.9.6  | Proper Transmission Line Terminations    | 543.e30 |

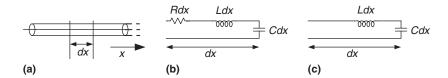

|      | A.9.7  | Derivation of $Z_0$                      | 543.e32 |

|      | A.9.8  | Derivation of the Reflection Coefficient | 543.e33 |

|      | A.9.9  | Putting It All Together                  | 543.e34 |

| A.10 | Econor | mics                                     | 543.e35 |

| Appe | ndix B | RISC-V Instruction Set Summary           | 544     |

| Anne | ndix C | C Programming                            | 545     |

|      |        |                                          |         |

| C.1  | Introd | uction                                   | 545     |

| Appe | ndix C | is available as an online supplement     | 545.e1  |

| C.1  | Introd | uction                                   | 545.e1  |

| C.2  | Welcon | ne to C                                  | 545.e3  |

|      | C.2.1  | C Program Dissection                     |         |

|      | C.2.2  | Running a C Program                      |         |

| C.3  |        | lation                                   |         |

|      | C.3.1  | Comments                                 |         |

|      | C.3.2  | #define                                  |         |

|      |        | Hinelude                                 |         |

| C.4   | Variable | es                                | <br>545.e7  |

|-------|----------|-----------------------------------|-------------|

|       | C.4.1    | Primitive Data Types              |             |

|       | C.4.2    | Global and Local Variables        |             |

|       | C.4.3    | Initializing Variables            | <br>545.e11 |

| C.5   | Operate  | ors                               |             |

| C.6   | Functio  | on Calls                          | <br>545.e15 |

| C.7   | Contro   | l-Flow Statements                 | <br>545.e16 |

|       | C.7.1    | Conditional Statements            | <br>545.e17 |

|       | C.7.2    | Loops                             | <br>545.e19 |

| C.8   | More D   | Oata Types                        | 545.e21     |

|       | C.8.1    | Pointers                          | <br>545.e21 |

|       | C.8.2    | Arrays                            | <br>545.e23 |

|       | C.8.3    | Characters                        | <br>545.e27 |

|       | C.8.4    | Strings                           | <br>545.e27 |

|       | C.8.5    | Structures                        | <br>545.e29 |

|       | C.8.6    | typedef                           | <br>545.e31 |

|       | C.8.7    | Dynamic Memory Allocation         | 545.e32     |

|       | C.8.8    | Linked Lists                      | <br>545.e33 |

| C.9   | Standar  | rd Libraries                      | <br>545.e35 |

|       | C.9.1    | stdio                             | <br>545.e35 |

|       | C.9.2    | stdlib                            | <br>545.e40 |

|       | C.9.3    | math                              | <br>545.e42 |

|       | C.9.4    | string                            | <br>545.e42 |

| C.10  | Compil   | er and Command Line Options       | <br>545.e43 |

|       | C.10.1   | Compiling Multiple C Source Files | <br>545.e43 |

|       | C.10.2   | Compiler Options                  | <br>545.e43 |

|       | C.10.3   | Command Line Arguments            | <br>545.e44 |

| C.11  | Commo    | on Mistakes                       | <br>545.e44 |

| Furth | er Read  | ing                               | <br>547     |

|       |          |                                   |             |

| Index |          |                                   | <br>549     |

#### **Preface**

This book is unique in its treatment in that it presents digital logic design from the perspective of computer architecture, starting at the beginning with 1's and 0's and leading through to the design of a microprocessor.

We believe that building a microprocessor is a special rite of passage for engineering and computer science students. The inner workings of a processor seem almost magical to the uninitiated yet prove to be straightforward when carefully explained. Digital design in and of itself is a powerful and exciting subject. Assembly language programming unveils the inner language spoken by the processor. Microarchitecture is the link that brings it all together.

The first two versions of this increasingly popular text cover the MIPS and ARM architectures. As one of the original Reduced Instruction Set Computing architectures, MIPS is clean and exceptionally easy to understand and build. MIPS remains an important architecture, as it has inspired many of the subsequent architectures, including RISC-V. The ARM architecture has exploded in popularity over the past several decades because of its efficiency and rich ecosystem. More than 50 billion ARM processors have been shipped, and more than 75% of humans on the planet use products with ARM processors.

Over the past decade, RISC-V has emerged as an increasingly important architecture, both pedagogically and commercially. As the first widely used open-source computer architecture, RISC-V offers the simplicity of MIPS with the flexibility and features of modern processors.

Pedagogically, the learning objectives of the MIPS, ARM, and RISC-V editions are identical. The RISC-V architecture has a number of features, including extendibility and compressed instructions, that contribute to its efficiency but add a small amount of complexity. The three microarchitectures are also similar, with MIPS and RISC-V architectures sharing many similarities. We expect to offer MIPS, ARM, and RISC-V editions as long as the market demands.

#### **FEATURES**

#### Side-by-Side Coverage of SystemVerilog and VHDL

Hardware description languages (HDLs) are at the center of modern digital design practices. Unfortunately, designers are evenly split between the two dominant languages, SystemVerilog and VHDL. This book introduces HDLs in Chapter 4 as soon as combinational and sequential logic design has been covered. HDLs are then used in Chapters 5 and 7 to design larger building blocks and entire processors. Nevertheless, Chapter 4 can be skipped and the later chapters are still accessible for courses that choose not to cover HDLs.

This book is unique in its side-by-side presentation of SystemVerilog and VHDL, enabling the reader to learn the two languages. Chapter 4 describes principles that apply to both HDLs, and then provides language-specific syntax and examples in adjacent columns. This side-by-side treatment makes it easy for an instructor to choose either HDL and for the reader to transition from one to the other, either in a class or in professional practice.

#### **RISC-V Architecture and Microarchitecture**

Chapters 6 and 7 offer in-depth coverage of the RISC-V architecture and microarchitecture. RISC-V is an ideal architecture because it is a real architecture shipped in an increasing number of commercial products, yet it is streamlined and easy to learn. Moreover, because of its popularity in the commercial and hobbyist worlds, simulation and development tools exist for the RISC-V architecture.

#### **Real-World Perspectives**

In addition to the real-world perspective in discussing the RISC-V architecture, Chapter 6 illustrates the architecture of Intel x86 processors to offer another perspective. Chapter 9 (available as an online supplement) also describes peripherals in the context of SparkFun's RED-V RedBoard, a popular development board that centers on SiFive's Freedom E310 RISC-V processor. These real-world perspective chapters show how the concepts in the chapters relate to the chips found in many PCs and consumer electronics.

#### **Accessible Overview of Advanced Microarchitecture**

Chapter 7 includes an overview of modern high-performance microarchitectural features, including branch prediction, superscalar, and out-of-order operation, multithreading, and multicore processors. The treatment is accessible to a student in a first course and shows how the microarchitectures in the book can be extended to modern processors.

#### **End-of-Chapter Exercises and Interview Questions**

The best way to learn digital design is to do it. Each chapter ends with numerous exercises to practice the material. The exercises are followed by a set of interview questions that our industrial colleagues have asked students who are applying for work in the field. These questions provide a helpful glimpse into the types of problems that job applicants will typically encounter during the interview process. Exercise solutions are available via the book's companion and instructor websites.

#### ONLINE SUPPLEMENTS

Supplementary materials are available online at ddcabook.com or the publisher's website: https://www.elsevier.com/books-and-journals/book-companion/9780128200643. These companion sites (accessible to all readers) include the following:

- Links to video lectures

- Solutions to odd-numbered exercises

- Figures from the text in PDF and PPTX formats

- ► Links to professional-strength computer-aided design (CAD) tools from Intel®

- ▶ Instructions on how to use PlatformIO (an extension of Visual Studio Code) to compile, assemble, and simulate C and assembly code for RISC-V processors

- ▶ Hardware description language (HDL) code for the RISC-V processor

- Intel's Quartus helpful hints

- Lecture slides in PowerPoint (PPTX) format

- Sample course and laboratory materials

- List of errata

The instructor site (accessible to instructors who register at https://inspectioncopy.elsevier.com) includes the following:

- Solutions to all exercises

- Laboratory solutions

#### **EdX MOOC**

This book also has a companion Massive Open Online Course (MOOC) through EdX. The course includes video lectures, interactive practice

problems, and interactive problem sets and labs. The MOOC is divided into two parts: Digital Design (ENGR 85A) and Computer Architecture (ENGR85B) offered by HarveyMuddX (on EdX, search for "Digital Design HarveyMuddX" and "Computer Architecture HarveyMuddX"). EdX does not charge for access to the videos but does charge for the interactive exercises and certificate. EdX offers discounts for students with financial need.

#### **HOW TO USE THE SOFTWARE TOOLS IN A COURSE**

#### **Intel's Quartus Software**

The Quartus software, either Web or Lite Edition, is a free version of Intel's professional-strength Quartus<sup>TM</sup> FPGA design tools. It allows students to enter their digital designs in schematic or using either the SystemVerilog or the VHDL hardware description language (HDL). After entering the design, students can simulate their circuits using the ModelSim<sup>TM</sup>-Intel FPGA Edition or Starter Edition, which is available with Intel's Quartus software. Quartus also includes a built-in logic synthesis tool that supports both SystemVerilog and VHDL.

The difference between the Web or Lite Edition and the Pro Edition is that the Web or Lite Edition supports a subset of the most common Altera FPGAs. The free versions of ModelSim degrade performance for simulations with more than 10,000 lines of HDL, whereas the professional version of ModelSim does not.

#### Platform10

PlatformIO, which is an extension of Visual Studio Code, serves as a soft-ware development kit (SDK) for RISC-V. With the explosion of SDKs for each new platform, PlatformIO has streamlined the process of programming and using various processors by providing a unified interface for a large number of platforms and devices. It is available as a free download and can be used with SparkFun's RED-V RedBoard, as described in the labs provided on the companion website. PlatformIO provides access to a commercial RISC-V compiler and allows students to write both C and assembly programs, compile them, and then run and debug them on SparkFun's RED-V RedBoard (see Chapter 9 and the accompanying labs).

#### **Venus RISC-V Assembly Simulator**

The Venus Simulator (available at: https://www.kvakil.me/venus/) is a web-based RISC-V assembly simulator. Programs are written (or copy/pasted) in the Editor tab and then simulated and run in the Simulator tab. Registers and memory contents can be viewed as the program runs.

PREFACE XXIII

#### **LABS**

The companion site includes links to a series of labs that cover topics from digital design through computer architecture. The labs teach students how to use the Quartus tools to enter, simulate, synthesize, and implement their designs. The labs also include topics on C and assembly language programming using PlatformIO and SparkFun's RED-V RedBoard.

After synthesis, students can implement their designs using the Altera DE2, DE2-115, DE0, or other FPGA board. The labs are written to target the DE2 or DE-115 boards. These powerful and competitively priced boards are available from de2-115.terasic.com. The board contains an FPGA that can be programmed to implement student designs. We provide labs that describe how to implement a selection of designs on the DE2-115 board using the Quartus software.

To run the labs, students will need to download and install Intel's Quartus Web or Lite Edition and Visual Studio Code with the PlatformIO extension. Instructors may also choose to install the tools on lab machines. The labs include instructions on how to implement the projects on the DE2/DE2-115 board. The implementation step may be skipped, but we have found it of great value. We have tested the labs on Windows, but the tools are also available for Linux.

#### **RVfpga**

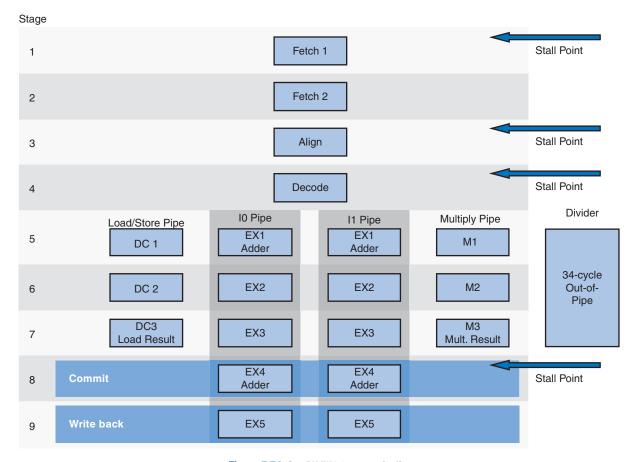

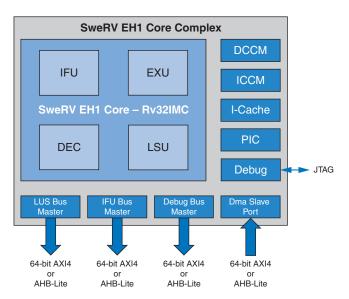

RISC-V FPGA, also referred to as RVfpga, is a free two-course sequence that can be completed after learning the material in this book. The first course shows how to target a commercial RISC-V core to an FPGA, program it using RISC-V assembly or C, add peripherals to it, and analyze and modify the core and memory system, including adding instructions to the core. This course uses the open-source SweRVolf system-on-chip (SoC) (https://github.com/chipsalliance/Cores-SweRVolf), which is based on Western Digital's open-source commercial SweRV EH1 core (https:// www.westerndigital.com/company/innovations/risc-v). The course also shows how to use Verilator, an open-source HDL simulator, and Western Digital's Whisper, an open-source RISC-V instruction set simulator (ISS). RVfpga-SoC, the second course, shows how to build an SoC based on SweRVolf using building blocks such as the SweRV EH1 core, interconnect, and memories. The course then guides the user in loading and running the Zephyr operating system on the RISC-V SoC. All necessary software and system source code (Verilog/SystemVerilog files) are free, and the courses may be completed in simulation, so no hardware is required. RVfpga materials are freely available with registration from the Imagination Technologies University Programme: https://university. imgtec.com/rvfpga/.

#### **BUGS**

As all experienced programmers know, any program of significant complexity undoubtedly contains bugs. So, too, do books. We have taken great care to find and squash the bugs in this book. However, some errors undoubtedly do remain. We will maintain a list of errata on the book's webpage.

Please send your bug reports to ddcabugs@gmail.com. The first person to report a substantive bug with a fix that we use in a future printing will be rewarded with a \$1 bounty!

#### **ACKNOWLEDGMENTS**

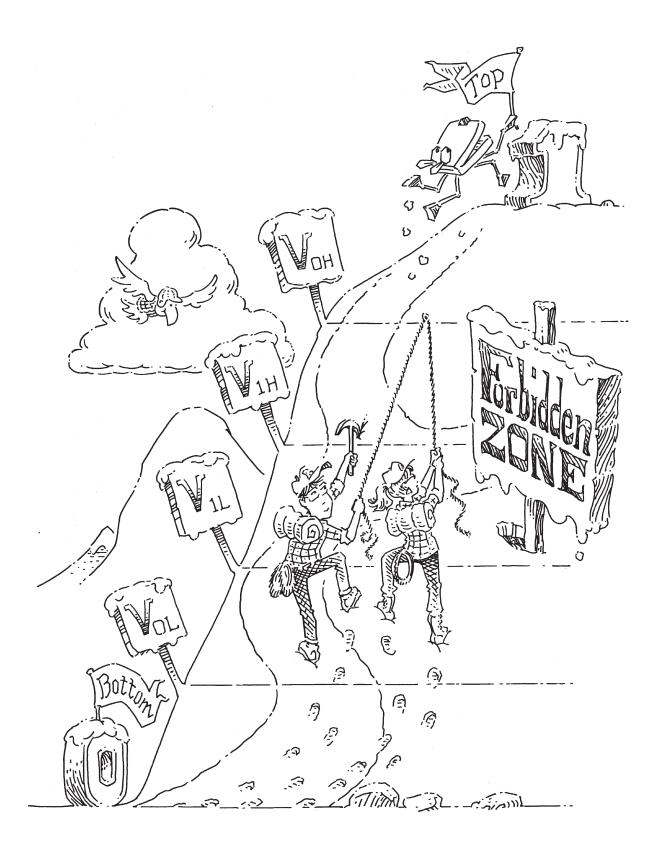

We appreciate the hard work of Steve Merken, Nate McFadden, Ruby Gammell, Andrae Akeh, Manikandan Chandrasekaran, and the rest of the team at Morgan Kaufmann who made this book happen. We love the art of Duane Bibby, whose cartoons enliven the chapters.

We thank Matthew Watkins, who contributed the section on Heterogeneous Multiprocessors in Chapter 7, and Josh Brake, who contributed to Chapter 9 on Embedded I/O Systems. We greatly appreciate the work of Mateo Markovic and Geordie Ryder, who reviewed the book and contributed to the exercise solutions. Numerous other reviewers also substantially improved the book. They include Daniel Chaver Martinez, Roy Kravitz, Zvonimir Bandic, Giuseppe Di Luna, Steffen Paul, Ravi Mittal, Jennifer Winikus, Hesham Omran, Angel Solis, Reiner Dizon, and Olof Kindgren. We also appreciate the students in our courses at Harvey Mudd College and UNLV who have given us helpful feedback on drafts of this textbook. And last, but not least, we both thank our families for their love and support.

#### **About the Authors**

Sarah L. Harris is an Associate Professor of Electrical and Computer Engineering at the University of Nevada, Las Vegas. She received her Ph.D. and M.S. in Electrical Engineering from Stanford University. Sarah has also worked with Hewlett-Packard, the San Diego Supercomputer Center, and NVIDIA. Sarah loves teaching, exploring and developing new technologies, traveling, playing the guitar and various other instruments, and spending time with her family. Her recent research includes designing bio-inspired prosthetics and implementing machine-learning algorithms in hardware.

David Harris is the Harvey S. Mudd Professor of Engineering Design and Associate Department Chair at Harvey Mudd College. He received his Ph.D. in electrical engineering from Stanford University and his M.Eng. in electrical engineering and computer science from MIT. Before attending Stanford, he worked at Intel as a logic and circuit designer on the Itanium and Pentium II processors. Since then, he has consulted at Broadcom, Sun Microsystems, Hewlett-Packard, Evans & Sutherland, and other design companies. David's passions include teaching, building chips and airplanes, and exploring the outdoors. When he is not at work, he can usually be found hiking, flying, and spending time with his family. David holds about a dozen patents and is the author of three other textbooks on chip design, as well as seven guidebooks to the Southern California mountains.

#### From Zero to One

## 1

#### 1.1 THE GAME PLAN

Microprocessors have revolutionized our world during the past three decades. A laptop computer today has far more capability than a room-sized mainframe of yesteryear. A luxury automobile contains about 100 microprocessors. Advances in microprocessors have made cell phones and the Internet possible, have vastly improved medicine, and have transformed how war is waged. Worldwide semiconductor industry sales have grown from US \$21 billion in 1985 to \$400 billion in 2020, and microprocessors are a major segment of these sales. We believe that microprocessors are not only technically, economically, and socially important, but are also an intrinsically fascinating human invention. By the time you finish reading this book, you will know how to design and build your own microprocessor. The skills you learn along the way will prepare you to design many other digital systems.

We assume that you have a basic familiarity with electricity, some prior programming experience, and a genuine interest in understanding what goes on under the hood of a computer. This book focuses on the design of digital systems, which operate on 1's and 0's. We begin with digital logic gates that accept 1's and 0's as inputs and produce 1's and 0's as outputs. We then explore how to combine logic gates into more complicated modules, such as adders and memories. Then, we shift gears to programming in assembly language, the native tongue of the microprocessor. Finally, we put gates together to build a microprocessor that runs these assembly language programs.

A great advantage of digital systems is that the building blocks are quite simple: just 1's and 0's. They do not require grungy mathematics or a profound knowledge of physics. Instead, the designer's challenge is to combine these simple blocks into complicated systems. A microprocessor may be the first system that you build that is too complex to fit in your

- 1.1 The Game Plan

- 1.2 The Art of Managing Complexity

- 1.3 The Digital Abstraction

- 1.4 Number Systems

- 1.5 Logic Gates

- 1.6 Beneath the Digital Abstraction

- 1.7 CMOS Transistors\*

- 1.8 Power Consumption\*

- 1.9 Summary and a Look Ahead Exercises

**Interview Questions**

head all at once. One of the major themes woven through this book is how to manage complexity.

#### 1.2 THE ART OF MANAGING COMPLEXITY

One of the characteristics that separates an engineer or computer scientist from a layperson is a systematic approach to managing complexity. Modern digital systems are built from millions or billions of transistors. No human being could understand these systems by writing equations describing the movement of electrons in each transistor and solving all of the equations simultaneously. You will need to learn to manage complexity to understand how to build a microprocessor without getting mired in a morass of detail.

#### 1.2.1 Abstraction

The critical technique for managing complexity is *abstraction*: hiding details when they are not important. A system can be viewed from many different levels of abstraction. For example, American politicians abstract the world into cities, counties, states, and countries. A county contains multiple cities and a state contains many counties. When a politician is running for president, the politician is mostly interested in how the state as a whole will vote rather than how each county votes, so the state is the most useful level of abstraction. On the other hand, the Census Bureau measures the population of every city, so the agency must consider the details of a lower level of abstraction.

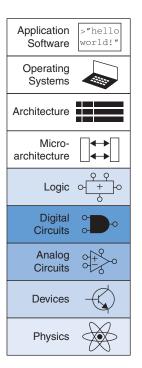

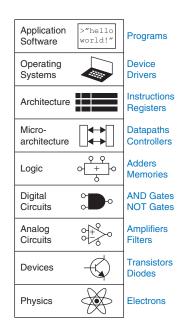

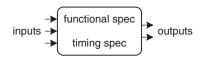

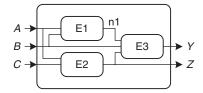

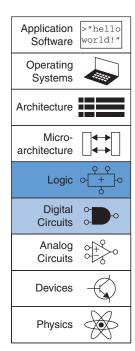

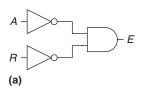

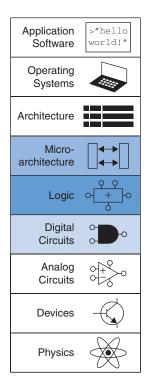

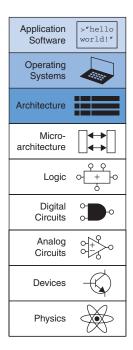

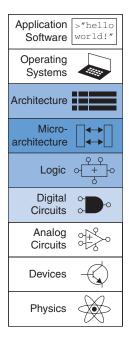

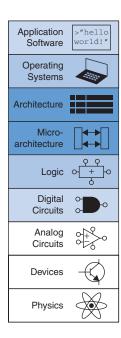

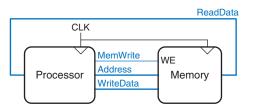

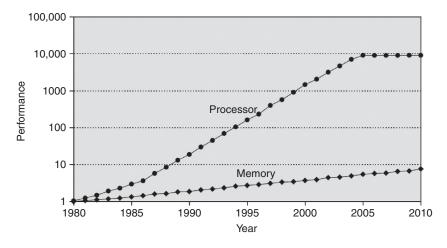

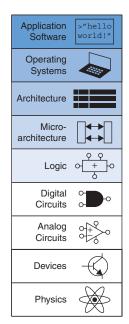

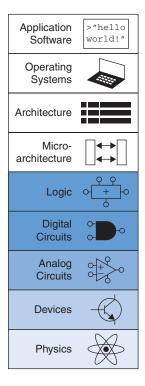

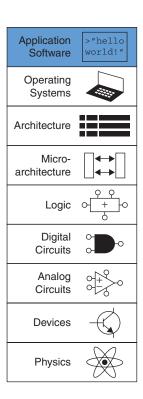

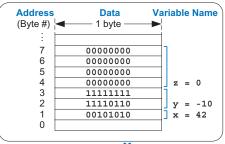

Figure 1.1 illustrates levels of abstraction for an electronic computer system, along with typical building blocks at each level. At the lowest level of abstraction is the physics, the motion of electrons. The behavior of electrons is described by quantum mechanics and Maxwell's equations. Our system is constructed from electronic *devices* such as transistors (or vacuum tubes, once upon a time). These devices have well-defined connection points called *terminals* and can be modeled by the relationship between voltage and current as measured at each terminal. By abstracting to this device level, we can ignore the individual electrons. The next level of abstraction is *analog circuits*, in which devices are assembled to create components such as amplifiers. Analog circuits input and output a continuous range of voltages. *Digital circuits*, such as logic gates, restrict the voltages to discrete ranges, which we will use to indicate 0 and 1. In logic design, we build more complex structures, such as adders or memories, from digital circuits.

Microarchitecture links the logic and architecture levels of abstraction. The architecture level of abstraction describes a computer from the programmer's perspective. For example, the Intel x86 architecture

Figure 1.1 Levels of abstraction for an electronic computing system

used by microprocessors in most *personal computers* (*PCs*) is defined by a set of instructions and registers (memory for temporarily storing variables) that the programmer is allowed to use. Microarchitecture involves combining logic elements to execute the instructions defined by the architecture. A particular architecture can be implemented by one of many different microarchitectures with different price/performance/power trade-offs. For example, the Intel Core i7, the Intel 80486, and the AMD Athlon all implement the x86 architecture with different microarchitectures.

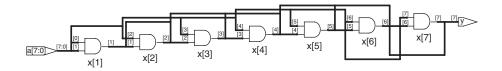

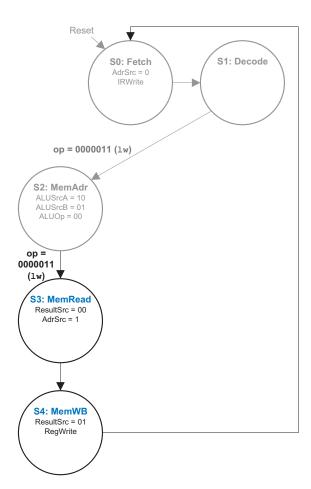

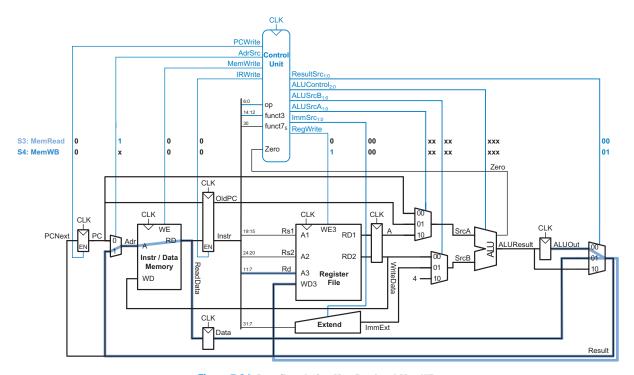

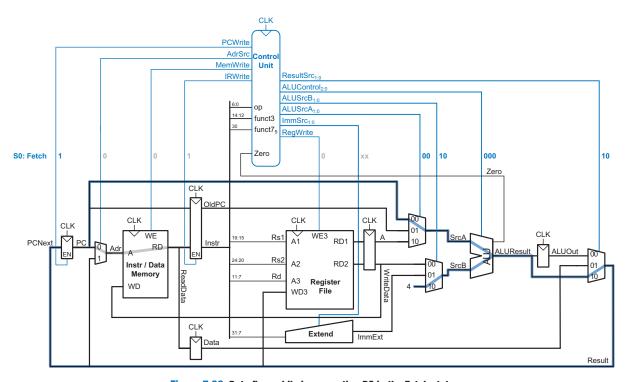

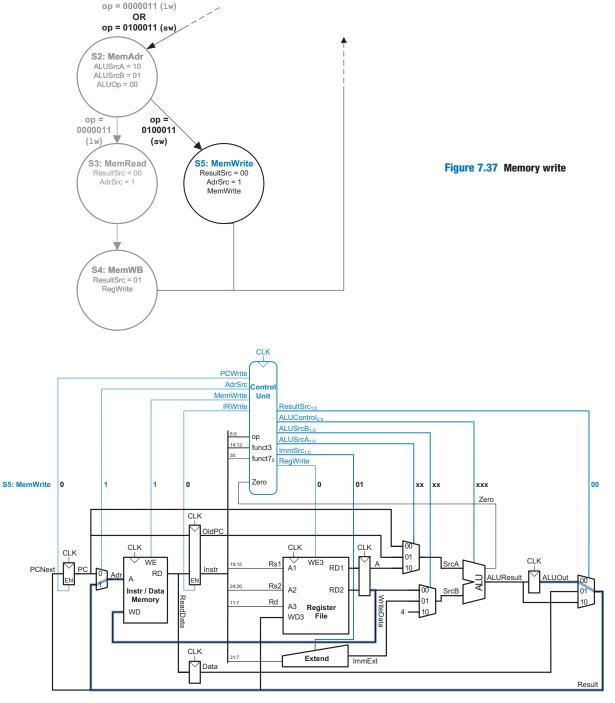

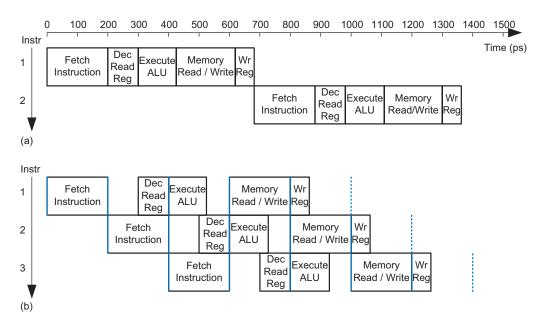

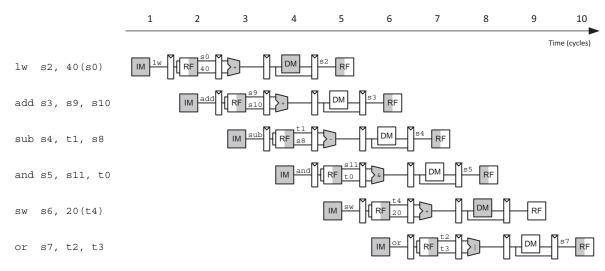

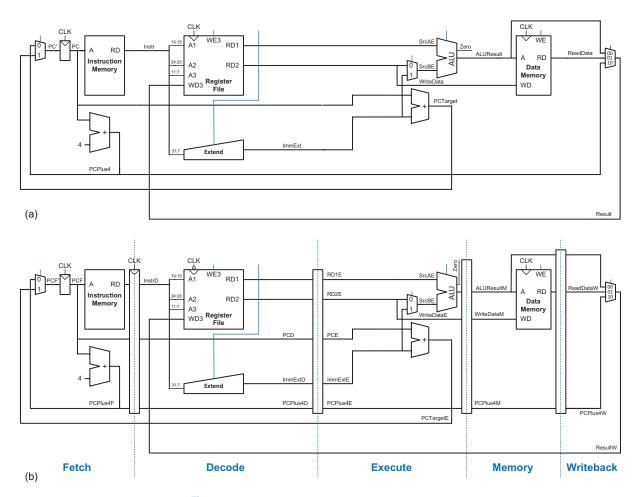

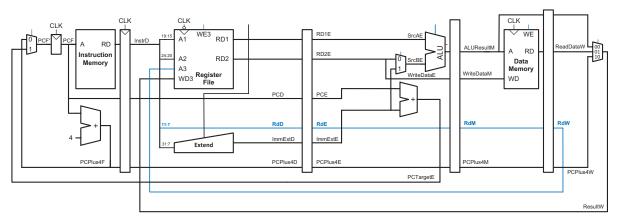

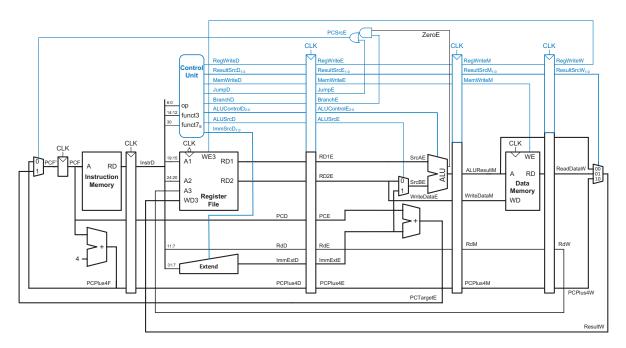

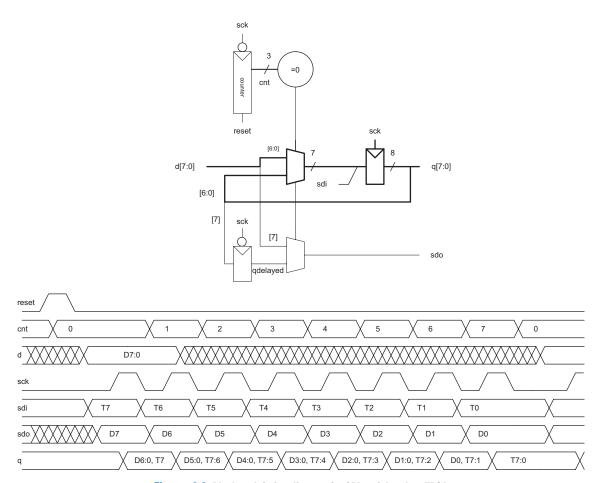

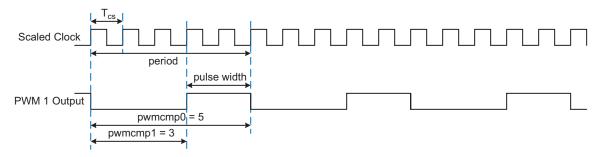

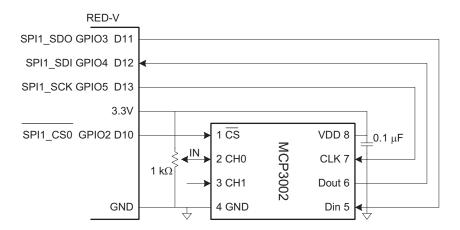

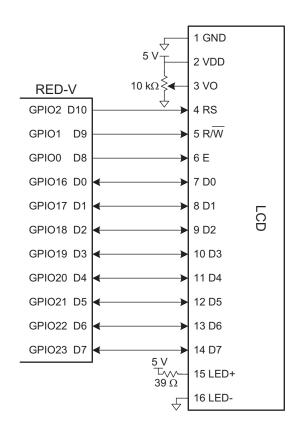

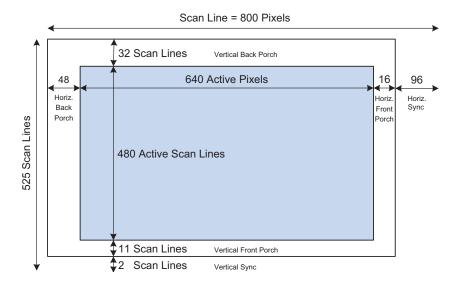

Moving into the software realm, the operating system handles low-level details, such as accessing a hard drive or managing memory. Finally, the application software uses these facilities provided by the operating system to solve a problem for the user. Thanks to the power of abstraction, your grandmother can surf the Web without any regard for the quantum vibrations of electrons or the organization of the memory in her computer.